# High-Speed Digital System Design

A Handbook of Interconnect Theory and Design Practices

> STEPHEN H. HALL GARRETT W. HALL JAMES A. McCALL

# High-Speed Digital System Design—A Handbook of Interconnect Theory and Design Practices

Stephen H. Hall Garrett W. Hall James A. McCall

New York • Chichester • Weinheim • Brisbane • Singapore • Toronto Copyright © 2000 by John Wiley & Sons, Inc.

All rights reserved.

No part of this publication may be reproduced, stored in a retrieval system or transmitted in any form or by any means, electronic, mechanical, photocopying, recording, scanning or otherwise, except as permitted under Sections 107 or 108 of the 1976 United States Copyright Act, without either the prior written permission of the Publisher, or authorization through payment of the appropriate per-copy fee to the Copyright Clearance Center, 222 Rosewood Drive, Danvers, MA 01923, (978) 750-8400, fax (978) 750-4744. Requests to the Publisher for permission should be addressed to the Permissions Department, John Wiley & Sons, Inc., 605 Third Avenue, New York, NY 10158-0012, (212) 850-6011, fax (212) 850-6008, E-Mail: PERMREQ@WILEY.COM.

For ordering and customer service, call 1-800-CALL-WILEY.

#### Library of Congress Cataloging-in-Publication Data:

Hall, Stephen H.

High-speed digital system design: a handbook of interconnect theory and design practices/Stephen H. Hall, Garrett W. Hall, James A. McCall p. cm.

ISBN 0-471-36090-2 (cloth)

1. Electronic digital computers—Design and construction.2. Very high speed integrated circuits—Design and construction.3. Microcomputers—Buses.4. Computer interfaces.I. Hall, Garrett W.II. McCall, James A.III. Title.

TK7888.3 H315 2000

621.39'8-dc21

00-025717

10987654321

# **Preface**

#### **Overview**

This book covers the practical and theoretical aspects necessary to design modern high-speed digital systems at the platform level. The book walks the reader through every required concept, from basic transmission line theory to digital timing analysis, high-speed measurement techniques, as well as many other topics. In doing so, a unique balance between theory and practical applications is achieved that will allow the reader not only to understand the nature of the problem, but also provide practical guidance to the solution. The level of theoretical understanding is such that the reader will be equipped to see beyond the immediate practical application and solve problems not contained within these pages. Much of the information in this book has not been needed in past digital designs but is absolutely necessary today. Most of the information covered here is not covered in standard college curricula, at least not in its focus on digital design, which is arguably one of the most significant industries in electrical engineering.

The focus of this book is on the design of robust high-volume, high-speed digital products such as computer systems, with particular attention paid to computer busses. However, the theory presented is applicable to any high-speed digital system. All of the techniques covered in this book have been applied in industry to actual digital products that have been successfully produced and sold in high volume.

Practicing engineers and graduate and undergraduate students who have completed basic electromagnetic or microwave design classes are equipped to fully comprehend the theory presented in this book. At a practical level, however, basic circuit theory is all the background required to apply the formulas in this book.

<u>Chapter 1</u> describes why it is important to comprehend the lessons taught in this book. (Authored by Garrett Hall)

<u>Chapter 2</u> introduces basic transmission line theory and terminology with specific digital focus. This chapter forms the basis of much of the material that follow. (Authored by Stephen Hall)

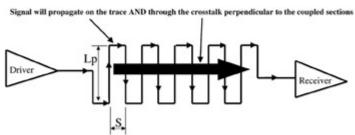

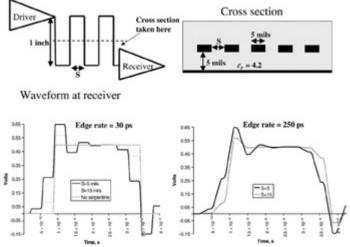

<u>Chapters 3</u> and <u>4</u> introduce crosstalk effects, explain their relevance to digital timings, and explore nonideal transmission line effects. (Authored by Stephen Hall)

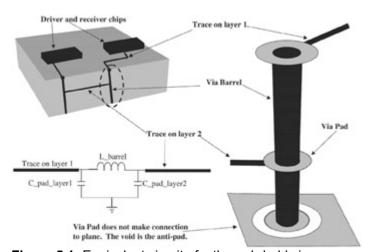

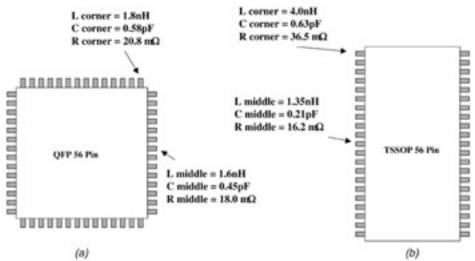

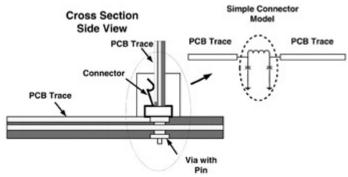

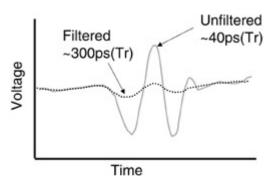

<u>Chapter 5</u> explains the impact of chip packages, vias, connectors, and many other aspects that affect the performance of a digital system. (Authored by Stephen Hall)

<u>Chapter 6</u> explains elusive effects such as simultaneous switching noise and nonideal current return path distortions that can devastate a digital design if not properly accounted for. (Authored by Stephen Hall)

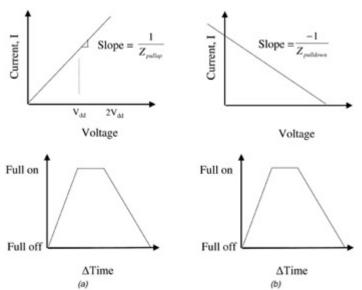

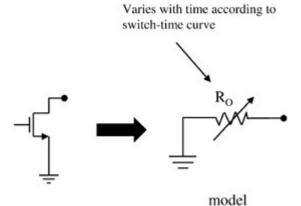

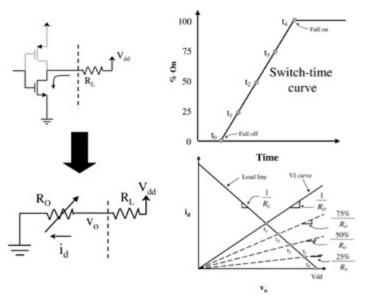

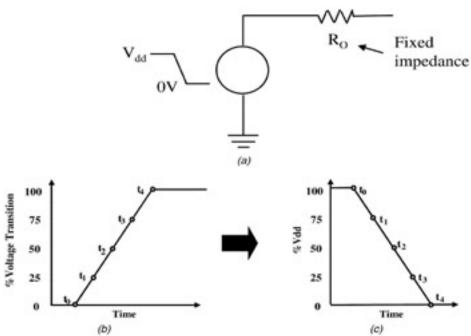

<u>Chapter 7</u> discusses different methods that can be used to model the output buffers that are used to drive digital signals onto a bus. (Authored by Garrett Hall)

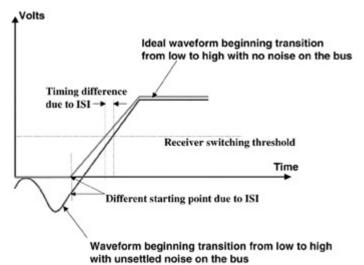

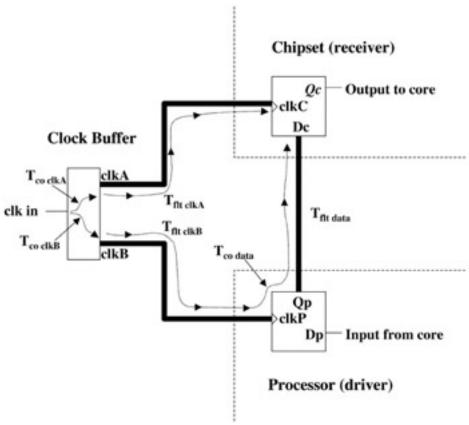

<u>Chapter 8</u> explains in detail several methods of system level digital timing. It describes the theory behind different timing schemes and relates them to the high-speed digital effects described throughout the book. (Authored by Stephen Hall)

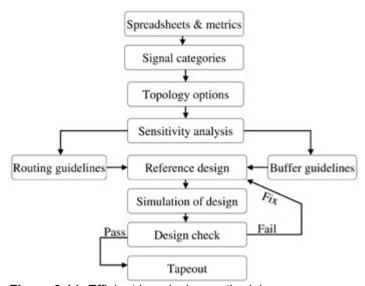

<u>Chapter 9</u> addresses one of the most far-reaching challenges that is likely to be encountered: handling the very large number of variables affecting a system and reducing them to a manageable methodology. This chapter explains how to make an intractable problem tractable. It introduces a specific design methodology that has been used to produce very high performance digital products. (Authored by Stephen Hall)

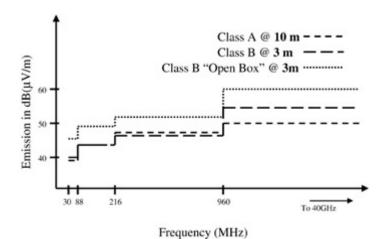

<u>Chapter 10</u> covers the subject of radiated emissions, which causes great fear in the hearts of system designers because radiated emission problems usually cannot be addressed until a prototype has been built, at which time changes can be very costly and time-constrained. (Authored by Garrett Hall)

<u>Chapter 11</u> covers the practical aspects of making precision measurements in high-speed digital systems. (Authored by James McCall)

## **Acknowledgments**

Many people have contributed directly or indirectly to this book. We have been fortunate to keep the company of excellent engineers and fine peers. Among the direct, knowing contributors to this book are:

- Dr. Maynard Falconer, Intel Corporation

- Mike Degerstrom, Mayo Foundation, Special Purpose Processor Development Group

- Dr. Jason Mix, Intel Corporation

- Dorothy Hall, PHI Incorporated

We would also like to recognize the following people for their continuing collaboration over the years, which have undoubtedly affected the outcome of this book. They have our thanks.

- Howard Heck, Intel Corporation; Oregon Graduate Institute

- Michael Leddige, Intel Corporation

- Dr. Tim Schreyer, Intel Corporation

- Harry Skinner, Intel Corporation

- Alex Levin, Intel Corporation

- Rich Melitz, Intel Corporation

- Wayne Walters, Mayo Foundation, Special Purpose Processor Development Group

- Pat Zabinski, Mayo Foundation, Special Purpose Processor Development Group

- Dr. Barry Gilbert, Mayo Foundation, Special Purpose Processor Development Group

- Dr. Melinda Picket-May, Colorado State University

Special thanks are also given to Jodi Hall, Stephen's wife, without whose patience and support this book would not have been possible.

# Chapter 1: The Importance of Interconnect Design

#### **OVERVIEW**

The speed of light is just too slow. Commonplace, modern, volume-manufactured digital designs require control of timings down to the picosecond range. The amount of time it takes light from your nose to reach your eye is about 100 picoseconds (in 100 ps, light travels about 1.2 in.). This level of timing must not only be maintained at the silicon level, but also at the physically much larger level of the system board, such as a computer motherboard. These systems operate at high frequencies at which conductors no longer behave as simple wires, but instead exhibit high-frequency effects and behave as transmission lines that are used to transmit or receive electrical signals to or from neighboring components. If these transmission lines are not handled properly, they can unintentionally ruin system timing. Digital design has acquired the complexity of the analog world and more. However, it has not always been this way. Digital technology is a remarkable story of technological evolution. It is a continuing story of paradigm shifts, industrial revolution, and rapid change that is unparalleled. Indeed, it is a common creed in marketing departments of technology companies that "by the time a market survey tells you the public wants something, it is already too late."

This rapid progress has created a roadblock to technological progress that this book will help solve. The problem is that modern digital designs require knowledge that has formerly not been needed. Because of this, many currently employed digital system designers do not have the knowledge required for modern high-speed designs. This fact leads to a surprisingly large amount of misinformation to propagate through engineering circles. Often, the concepts of high-speed design are perceived with a sort of mysticism. However, this problem has not come about because the required knowledge is unapproachable. In fact, many of the same concepts have been used for several decades in other disciplines of electrical engineering, such as radio-frequency design and microwave design. The problem is that most references on the necessary subjects are either too abstract to be immediately applicable to the digital designer, or they are too practical in nature to contain enough theory to fully understand the subject. This book will focus directly on the area of digital design and will explain the necessary concepts to understand and solve contemporary and future problems in a manner directly applicable by practicing engineers and/or students. It is worth noting that everything in this book has been applied to a successful modern design.

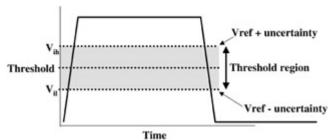

#### 1.1. THE BASICS

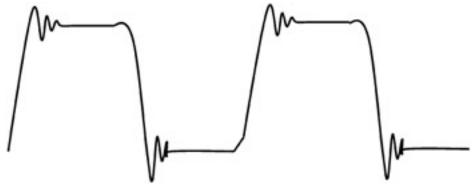

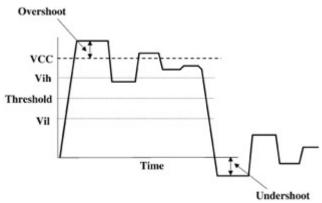

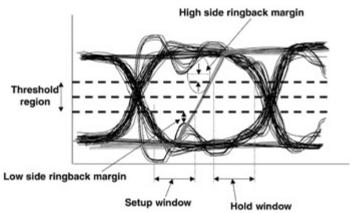

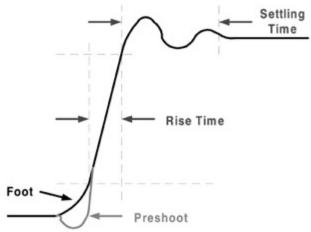

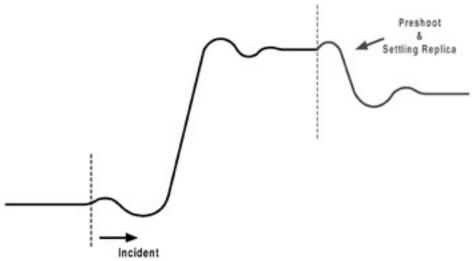

As the reader undoubtedly knows, the basic idea in digital design is to communicate information with signals representing 1s or 0s. Typically this involves sending and receiving a series of trapezoidal shaped voltage signals such as shown in Figure 1.1 in which a high voltage is a 1 and a low voltage is a 0. The conductive paths carrying the digital signals are known as interconnects. The interconnect includes the entire electrical pathway from the chip sending a signal to the chip receiving the signal. This includes the chip packages, connectors, sockets, as well as a myriad of additional structures. A group of interconnects is referred to as a bus. The region of voltage where a digital receiver distinguishes between a high and a low voltage is known as the threshold region. Within this region, the receiver will either switch high or switch low. On the silicon, the actual switching voltages vary with temperature, supply voltage, silicon process, and other variables. From the system designers point of view, there are usually high-and low-voltage thresholds, known as Vih and Vil, associated with the receiving silicon, above which and below which a high or low value can be guaranteed to be received under all conditions. Thus the designer must guarantee that the system can, under all conditions, deliver high voltages that do not, even briefly, fall below Vih, and low voltages that remain below Vil, in order to ensure the integrity of the data.

Figure 1.1: Digital waveform.

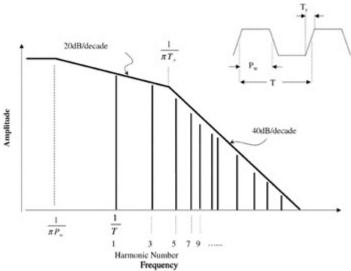

In order to maximize the speed of operation of a digital system, the timing uncertainty of a transition through the threshold region must be minimized. This means that the rise or fall time of the digital signal must be as fast as possible. Ideally, an infinitely fast edge rate would be used, although there are many practical problems that prevent this. Realistically, edge rates of a few hundred picoseconds can be encountered. The reader can verify with Fourier analysis that the quicker the edge rate, the higher the frequencies that will be found in the spectrum of the signal. Herein lies a clue to the difficulty. Every conductor has a capacitance, inductance, and frequency-dependent resistance. At a high enough frequency, none of these things is negligible. Thus a wire is no longer a wire but a distributed parasitic element that will have delay and a transient impedance profile that can cause distortions and glitches to manifest themselves on the waveform propagating from the driving chip to the receiving chip. The wire is now an element that is coupled to everything around it, including power and ground structures and other traces. The signal is not contained entirely in the conductor itself but is a combination of all the local electric and magnetic fields around the conductor. The signals on one interconnect will affect and be affected by the signals on another. Furthermore, at high frequencies, complex interactions occur between the different parts of the same interconnect, such as the packages, connectors, vias, and bends. All these high-speed effects tend to produce strange, distorted waveforms that will indeed give the designer a completely different view of high-speed logic signals. The physical and electrical attributes of every structure in the vicinity of the interconnect has a vital role in the simple task of guaranteeing proper signaling transitions through Vih and Vil with the appropriate timings. These things also determine how much energy the system will radiate

into space, which will lead to determining whether the system complies with governmental emission requirements. We will see in later chapters how to account for all these things.

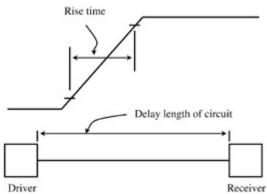

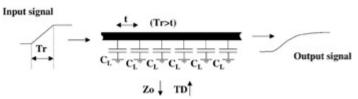

When a conductor must be considered as a distributed series of inductors and capacitors, it is known as a *transmission line*. In general, this must be done when the physical size of the circuit under consideration approaches the wavelength of the highest frequency of interest in the signal. In the digital realm, since edge rate pretty much determines the maximum frequency content, one can compare rise and fall times to the size of the circuit instead, as shown in <u>Figure 1.2</u>. On a typical circuit board, a signal travels about half the speed of light (exact formulas will be in later chapters). Thus a 500 ps edge rate occupies about 3 in. in length on a circuit trace. Generally, any circuit length at least 1/10th of the edge rate must be considered as a transmission line.

Figure 1.2: Rise time and circuit length.

One of the most difficult aspects of high-speed design is the fact that there are a large number codependent variables that affect the outcome of a digital design. Some of the variables are controllable and some force the designer to live with the random variation. One of the difficulties in high-speed design is how to handle the many variables, whether they are controllable or uncontrollable. Often simplifications can be made by neglecting or assuming values for variables, but this can lead to unknown failures down the road that will be impossible to "root cause" after the fact. As timing becomes more constrained, the simplifications of the past are rapidly dwindling in utility to the modern designer. This book will also show how to incorporate a large number of variables that would otherwise make the problem intractable. Without a methodology for handling the large amount of variables, a design ultimately resorts to guesswork no matter how much the designer physically understands the system. The final step of handling all the variables is often the most difficult part and the one most readily ignored by a designer. A designer crippled by an inability to handle large amounts of variables will ultimately resort to proving a few "point solutions" instead and hope that they plausibly represent all known conditions. While sometimes such methods are unavoidable, this can be a dangerous guessing game. Of course, a certain amount of guesswork is always present in a design, but the goal of the system designer should be to minimize uncertainty.

#### 1.2. THE PAST AND THE FUTURE

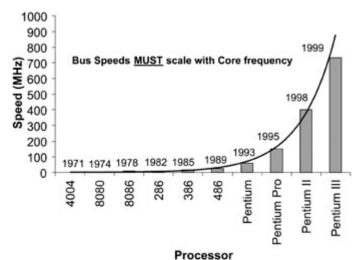

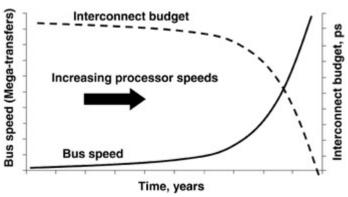

Gordon Moore, co-founder of Intel Corporation, predicted that the performance of computers will double every 18 months. History confirmed this insightful prediction. Remarkably, computer performance has doubled approximately every 1.5 years, along with substantial decreases in their price. One measure of relative processor performance is internal clock rates. Figure 1.3 shows several processors through history and their associated internal clock rates. By the time this is in print, even the fastest processors on this chart will likely be considered unimpressive. The point is that computer speeds are increasing exponentially. As core frequency increases, faster data rates will be demanded from the buses that feed information to the processor, as shown in Figure 1.4, leading to an interconnect timing budget that is decreasing exponentially. Decreased timing budgets mean that it is evermore important to properly account for any phenomenon that may increase the timing uncertainty of the digital waveform as it arrives at the receiver. This is the root cause of two inescapable obstacles that will continue to make digital system design difficult. The first obstacle is simply that the sheer amount of variables that must be accounted for in a digital design is increasing. As frequencies increase, new effects, which may have been negligible at slower speeds, start to become significant. Generally speaking, the complexity of a design increases exponentially with increasing variable count. The second obstacle is that the new effects, which could be ignored in designs of the past, must be modeled to a very high precision. Often these new models are required to be three-dimensional in nature, or require specialized analog techniques that fall outside the realms of the digital designer's discipline. The obstacles are perhaps more profound on the subsystems surrounding the processor since they evolve at a much slower rate, but still must support the increasing demands of the processor.

Figure 1.3: Moore's law in action.

**Figure 1.4:** The interconnect budget shrinks as the performance and frequency of the system increases.

All of this leads to the present situation: There are new problems to solve. Engineers who can solve these problems will define the future. This book will equip the reader with the necessary practical understanding to contend with modern high-speed digital design and with enough theory to see beyond this book and solve problems that the authors have not yet encountered. Read on.

# **Chapter 2: Ideal Transmission Line Fundamentals**

In today's high-speed digital systems, it is necessary to treat the printed circuit board (PCB) or multichip module (MCM) traces as transmission lines. It is no longer possible to model interconnects as lumped capacitors or simple delay lines, as could be done on slower designs. This is because the timing issues associated with the transmission lines are becoming a significant percentage of the total timing margin. Great attention must be given to the construction of the PCB so that the electrical characteristics of the transmission lines are controlled and predictable. In this chapter we introduce the basic transmission line structures typically used in digital systems and present basic transmission line theory for the ideal case. The material presented in this chapter provides the necessary knowledge base needed to comprehend all subsequent chapters.

#### 2.1. TRANSMISSION LINE STRUCTURES ON A PCB OR MCM

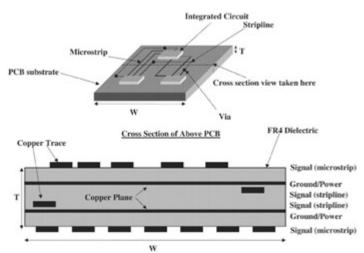

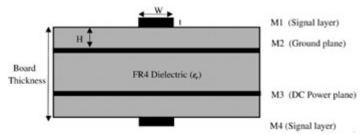

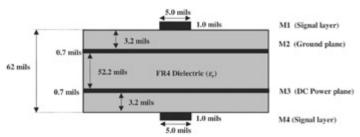

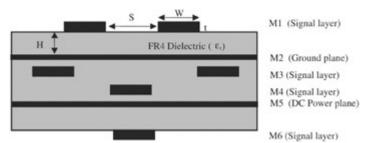

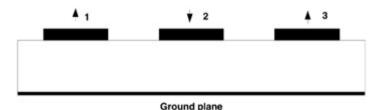

Transmission line structures seen on a typical PCB or MCM consist of conductive traces buried in or attached to a dielectric or insulating material with one or more reference planes. The metal in a typical PCB is usually copper and the dielectric is FR4, which is a type of fiberglass. The two most common types of transmission lines used in digital designs are microstrips and striplines. A *microstrip* is typically routed on an outside layer of the PCB and has only one reference plane. There are two types of microstrips, buried and nonburied. A *buried* (sometimes called *embedded*) *microstrip* is simply a transmission line that is embedded into the dielectric but still has only one reference plane. A *stripline* is routed on an inside layer and has two reference planes. Figure 2.1 represents a PCB with traces routed between the various components on both internal (stripline) and external (microstrip) layers. The accompanying cross section is taken at the given mark so that the position of transmission lines relative to the ground/power planes can be seen. In this book, transmission lines are often represented in the form of a cross section. This is very useful for calculating and visualizing the various transmission line parameters described later.

Figure 2.1: Example transmission lines in a typical design built on a PCB.

Multiple-layer PCBs such as the one depicted in <u>Figure 2.1</u> can provide a variety of stripline and microstrip structures. Control of the conductor and dielectric layers (which is referred to as the *stackup*) is required to make the electrical characteristics of the transmission line predictable. In high-speed systems, control of the electrical characteristics of the

transmission lines is crucial. These basic electrical characteristics, defined in this chapter, will be referred to as *transmission line parameters*.

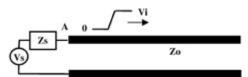

#### 2.2. WAVE PROPAGATION

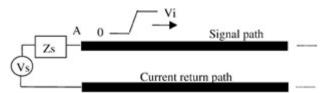

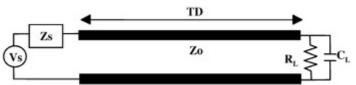

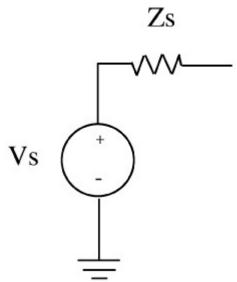

At high frequencies, when the edge rate (rise and fall times) of the digital signal is small compared to the propagation delay of an electrical signal traveling down the PCB trace, the signal will be greatly affected by transmission line effects. The electrical signal will travel down the transmission line in the way that water travels through a long square pipe. This is known as *electrical wave propagation*. Just as the waterfront will travel as a wave down the pipe, an electrical signal will travel as a wave down a transmission line. Additionally, just as the water will travel the length of the pipe in a finite amount of time, the electrical signal will travel the length of the transmission line in a finite amount of time. To take this simple analogy one step further, the voltage on a transmission line can be compared to the height of the water in the pipe, and the flow of the water can be compared to the current. Figure 2.2 depicts a common way of representing a transmission line. The top line is the signal path and the bottom line is the current return path. The voltage  $V_i$  is the initial voltage launched onto the line at node A, and  $V_s$  and  $Z_s$  form a Thévenin equivalent representation of the output buffer, usually referred to as the *source* or the *driver*.

**Figure 2.2:** Typical method of portraying a digital signal propagating on a transmission line.

#### 2.3. TRANSMISSION LINE PARAMETERS

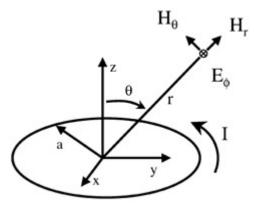

To analyze the effects that transmission lines have on high-speed digital systems, the electrical characteristics of the line must be defined. The basic electrical characteristics that define a transmission line are its characteristic impedance and its propagation velocity. The characteristic impedance is similar to the width of the water pipe used in the analogy above. and the propagation velocity is simply analogous to speed at which the water flows through the pipe. To define and derive these terms, it is necessary to examine the fundamental properties of a transmission line. As a signal travels down the transmission line depicted in Figure 2.2, there will be a voltage differential between the signal path and the current return path (generically referred to as a ground return path or an ac ground even when the reference plane is a power plane). When the signal reaches an arbitrary point z on the transmission line, the signal path conductor will be at a potential of V<sub>i</sub> volts and the ground return conductor will be at a potential of 0 V. This voltage difference establishes an electric field between the signal and the ground return conductors. Furthermore, Ampère's law states that the line integral of the magnetic field taken about any given closed path must be equal to the current enclosed by that path. In simpler terms, this means that if a current is flowing through a conductor, it results in a magnetic field around that conductor. We have therefore established that if an output buffer injects a signal of voltage  $V_i$  and current  $I_i$  onto a transmission line, it will induce an electric and a magnetic field, respectively. However, it should be clear that the voltage  $V_i$  and current  $I_i$ , at any arbitrary point on the line z will be zero until the time z/v, where v is the velocity of the signal traveling down the transmission line and z is the distance from the source. Note that this analysis implies that the signal is not simply traveling on the signal conductor of the transmission line; rather, it is traveling between the signal conductor and reference plane in the form of an electric and a magnetic field.

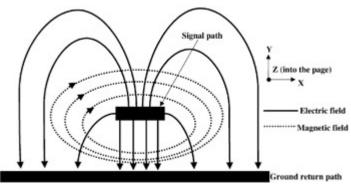

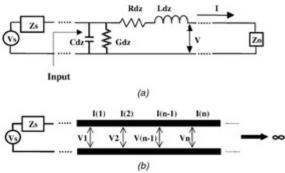

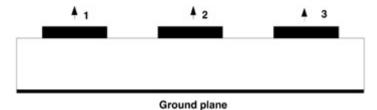

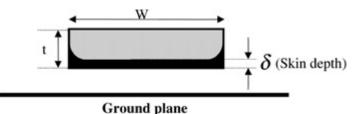

Now that the basic electromagnetic properties of a transmission line have been established, it is possible to construct a simple circuit model for a section of the line. Figure 2.3 represents a cross section of a microstrip transmission line and the electric and magnetic field patterns associated with a current flowing though the line. If it is assumed that there are no components of the electric or magnetic fields propagating in the z-direction (into the page), the electric and magnetic fields will be orthogonal. This is known as transverse electro-magnetic mode (TEM). Transmission lines will propagate in TEM mode under normal circumstances and it is an adequate approximation even at relatively high frequencies. This allows us to examine the transmission line in differential sections (or slices) along the length of the line traveling in the z-direction (into the page). The two components shown in Figure 2.3 are the electric and magnetic fields for an infinitesimal or differential section (slice) of the transmission line of length dz. Since there is energy stored in both an electric and a magnetic field, let us include the circuit components associated with this energy storage in our circuit model. The magnetic field for a differential section of the transmission line can be represented by a series inductance Ldz, where L is inductance per length. The electric field between the signal path and the ground path for a length of dz can be represented by a shunt capacitor C dz, where C is capacitance per length. An ideal model would consist of an infinite number of these small sections cascaded in series. This model adequately describes a section of a loss-free transmission line (i.e., a transmission line with no resistive losses).

**Figure 2.3:** Cross section of a microstrip depicting the electric and magnetic fields assuming that an electrical signal is propagating down the line into the page.

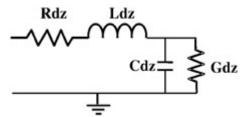

However, since the metal used in PCB boards is not infinitely conductive and the dielectrics are not infinitely resistive, loss mechanisms must be added to the model in the form of a series resistor, R dz, and a shunt resistor to ground referred to as a conductance, G dz, with units of siemens (1/ohm). Figure 2.4 depicts the equivalent circuit model for a differential section of a transmission line. The series resistor, R dz, represents the losses due to the finite conductivity of the conductor; the shunt resistor, G dz, represents the losses due to the finite resistance of the dielectric separating the conductor and the ground plane, the series inductor, Ldz, represents the magnetic field; and the capacitor, C dz, represents the electric field between the conductor and the ground plane. In the remainder of this book, one of these sections will be known as an RLCG element.

**Figure 2.4:** Equivalent circuit model of a differential section of a transmission line of length dz (RLCG model).

## 2.3.1. Characteristic Impedance

The characteristic impedance  $Z_o$  of the transmission line is defined by the ratio of the voltage and current waves at any point of the line; thus,  $VI = Z_o$ . Figure 2.5 depicts two representations of a transmission line. Figure 2.5a represents a differential section of a transmission line of length dz modeled with an RLCG element as described above and terminated in an impedance of  $Z_o$ . The characteristic impedance of the RLCG element is defined as the ratio of the voltage V and current I, as depicted in Figure 2.5a. Assuming that the load  $Z_o$  is exactly equal to the characteristic impedance of the RLCG element, Figure 2.5a can be represented by Figure 2.5b, which is an infinitely long transmission line. The termination,  $Z_o$ , in Figure 2.5a simply represents the infinite number of additional RLCG segments of impedance  $Z_o$  that comprise the complete transmission line model. Since the voltage/current ratio in the terminating device,  $Z_o$ , will be the same as that in the RLCG segment, then from the perspective of the voltage source, Figure 2.5a and D will be indistinguishable. With this simplification, the characteristic impedance can be derived for an infinitely long transmission line.

**Figure 2.5:** Method of deriving a transmission lines characteristic impedance: (a) differential section; (b) infinitely long transmission line.

To derive the characteristic impedance of the line, <u>Figure 2.5a</u> should be examined. Solving the equivalent circuit of <u>Figure 2.5a</u> for the input impedance with the assumption that the characteristic impedance of the line is equal to the terminating impedance,  $Z_o$ , yields <u>equation (2.1)</u>. For simplicity, the differential length dz is replaced with a short length of  $\Delta z$ . The derivation is as follows: Let

$$jwL(\Delta z) + R(\Delta z) = Z\Delta z$$

(series impedance for length of line  $\Delta z$ )

$jwC(\Delta z) + G(\Delta z) = Y\Delta z$  (parallel admittance for length of line  $\Delta z$ )

Then

$$\begin{split} Z(\text{input}) &= Z_o = \frac{(Z_o + Z \Delta z)(1/Y \Delta z)}{Z_o + Z \Delta z + 1/Y \Delta z} & \text{(assuming the load is equal to the characteristic impedance)} \\ Z_o\left(Z \Delta z + Z_o + \frac{1}{Y \Delta z}\right) &= (Z_o + Z \Delta z)\frac{1}{Y \Delta z} \\ &\Rightarrow Z_o Z \Delta z + Z_o^2 + \frac{Z_o}{Y \Delta z} = \frac{Z_o}{Y \Delta z} + \frac{Z \Delta z}{Y \Delta z} \\ &\Rightarrow Z_o(Z \Delta z + Z_o) = \frac{Z}{Y} \\ &\Rightarrow Z_o Y (Z \Delta z + Z_o) = Z \\ &\Rightarrow \lim_{z \to z} [Z] &= Z_o^2 Y \end{split}$$

$$Z_{o}=\sqrt{\frac{Z}{Y}}=\sqrt{\frac{R+j\omega L}{G+j\omega C}}$$

where R is in ohms per unit length, L is in henries per unit length, G is in siemens per unit length, C is in farads per unit length, and W is in radians per second. It is usually adequate to

approximate the characteristic impedance as  $Z_o = \sqrt{L/C}$ , since R and G both tend to be significantly smaller than the other terms. Only at very high frequencies, or with very lossy lines, do the R and G components of the impedance become significant. (Lossy transmission lines are covered in Chapter 4). Lossy lines will also yield complex characteristic impedances (i.e., having imaginary components). For the purposes of digital design, however, only the magnitude of the characteristic impedance is important.

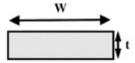

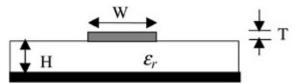

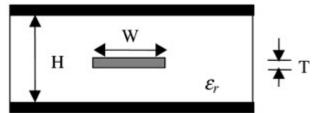

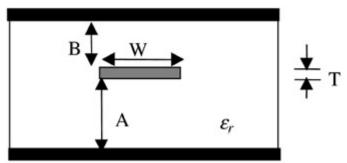

For maximum accuracy, it is necessary to use one of the many commercially available two-dimensional electromagnetic field solvers to calculate the impedance of the PCB traces for design purposes. The solvers will typically provide the impedance, propagation velocity, and L and C elements per unit length. This is adequate since R and G usually have a minimal effect on the impedance. In the absence of a field solver, the formulas presented in Figure 2.6 will provide good approximations to the impedance values of typical transmission lines as a function of the trace geometry and the dielectric constant ( $\varepsilon_r$ ). More accurate formulas for characteristic impedance are presented in Appendix A.

$$\begin{array}{c|c} & & & & \\ & & & \\ & & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\$$

**Figure 2.6:** Characteristic impedance approximations for typical transmission lines: (a) microstrip line; (b) symmetrical stripline; (c) offset stripline.

## 2.3.2. Propagation Velocity, Time, and Distance

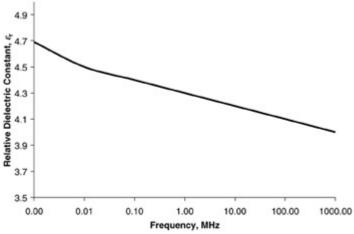

Electrical signals on a transmission line will propagate at a speed that depends on the surrounding medium. Propagation delay is usually measured in terms of seconds per meter and is the inverse of the propagation velocity. The propagation delay of a transmission line will increase in proportion to the square root of the surrounding dielectric constant. The time delay of a transmission line is simply the amount of time it takes for a signal to propagate the entire length of the line. The following equations show the relationships between the dielectric constant, the propagation velocity, the propagation delay, and the time delay:

(2.2)

$$v = \frac{c}{\sqrt{\varepsilon_r}}$$

(2.3)  $PD = \frac{1}{v} = \frac{\sqrt{\varepsilon_r}}{c}$

(2.4)  $TD = \frac{x\sqrt{\varepsilon_r}}{c}$

where

v = propagation velocity, in meters/second

c = speed of light in a vacuum (3 × 10<sup>8</sup> m/s)

$\varepsilon_r$  = dielectric constant

PD = propagation delay, in seconds per meter

TD = time delay for a signal to propagate down a transmission line of length x

x = length of the transmission line, in meters

The time delay can also be determined from the equivalent circuit model of the transmission line:

(2.5) TD =

$$\sqrt{LC}$$

where L is the total series inductance for the length of the line and C is the total shunt capacitance for the length of the line.

It should be noted that equations (2.2) through (2.4) assume that no magnetic materials are present, such that  $\mu_r$  = 1, and thus effects due to magnetic materials can be left out of the formulas.

The delay of a transmission line depends on the dielectric constant of the dielectric material, the line length, and the geometry of the transmission line cross section. The cross-sectional geometry determines whether the electric field will stay completely contained within the board or fringe out into the air. Since a typical PCB board is made out of FR4, which has a dielectric constant of approximately 4.2, and air has a dielectric constant of 1.0, the resulting "effective" dielectric constant will be a weighted average between the two. The amount of the electric field that is in the FR4 and the amount that is in the air determine the effective value. When the electric field is completely contained within the board, as in the case of a stripline, the effective dielectric constant will be larger and the signals will propagate more slowly than will externally routed traces. When signals are routed on the external layers of the board as in the case of a microstrip line, the electric field fringes through the dielectric material and the air, which lowers the effective dielectric constant; thus the signals will propagate more quickly than those on an internal layer.

The effective dielectric constant for a microstrip is calculated as follows [Collins, 1992]:

(2.6)

$$\varepsilon_e = \frac{\varepsilon_r + 1}{2} + \frac{\varepsilon_r - 1}{2} \left( 1 + \frac{12H}{W} \right)^{-1/2} + F - 0.217(\varepsilon_r - 1) \frac{T}{\sqrt{WH}}$$

(2.7)

$$F = \begin{cases} 0.02(\varepsilon_r - 1) \left( 1 - \frac{W}{H} \right)^2 & \text{for } \frac{W}{H} < 1 \\ 0 & \text{for } \frac{W}{H} > 1 \end{cases}$$

where  $\varepsilon_r$  is the dielectric constant of the board material, H the height of the conductor above the ground plane, W the conductor width, and T the conductor thickness.

# 2.3.3. Equivalent Circuit Models for SPICE Simulation

In Section 2.3 we introduced the equivalent distributed circuit model of a transmission line, which consisted of an infinite number of RLCG segments cascaded together. Since it is not practical to model a transmission line with an infinite number of elements, a sufficient number can be determined based on the minimum rise or fall time used in the simulation. When simulating a digital system, it is usually sufficient to choose the values so that the time delay  $(TD = \sqrt{LC})$  of the shortest RLCG segment is no larger than one-tenth of the minimum system rise or fall time. The rise or fall time is defined as the amount of time it

takes a signal to transition between its minimum and maximum magnitude. Rise times are typically measured between the 10 and 90% values of the maximum swing. For example, if a signal transitioned from 0 V to 1 V, its rise time would be measured between the times when the voltage reaches 0.1 and 0.9 V.

#### **RULE OF THUMB: Choosing a Sufficient Number of RLCG Segments**

When using a distributed *RLCG* model for modeling transmission lines, the number of *RLCG* segments should be determined as follows:

segments

$$\geq 10 \left( \frac{x}{T_r v} \right)$$

where x is the length of the line, v the propagation velocity of the transmission line, and  $T_r$  the rise (or fall) time. Each parasitic in the model should be scaled by the number of segments. For example, if the parasitics are known per unit meter, the maximum values used for a single segment must be

$$C_{

m segment} = rac{(x)(C/{

m meter})}{{

m segments}}$$

$L_{

m segment} = rac{(x)L/{

m meter}}{{

m segments}}$

$R_{

m segment} = rac{(x)R/{

m meter}}{{

m segments}}$

$G_{

m segment} = rac{(x)R/{

m meter}}{{

m segments}}$

$TD_{

m segment} = \sqrt{L_{

m segment}}C_{

m segment} \leq rac{T_r}{10}$

#### **Example 2.1: Creating a Transmission Line Model.**

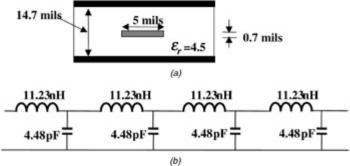

Create an equivalent circuit model of a loss-free  $50-\Omega$  transmission line 5 in. long for the cross section shown in <u>Figure 2.7a</u>. Assume that the driver has a minimum rise time of 2.5 ns. Assume a dielectric constant of 4.5.

Figure 2.7: Creating a transmission line model: (a) cross section; (b) equivalent circuit.

SOLUTION: Initially, the inductance and capacitance of the transmission line must be calculated. Since no field solver is available, the equations presented above will be used.

$$Z_o \approx \frac{60}{\sqrt{\varepsilon_r}} \ln \frac{4H}{0.67\pi(T+0.8W)} = \frac{60}{\sqrt{\varepsilon_r}} \ln \frac{4(14.7)}{0.67\pi[0.7+0.8(5)]} = 50 \Omega$$

$TD = \frac{x\sqrt{\varepsilon_r}}{c} = 5 \text{ in.}(0.0254 \text{ m/in.}) \frac{\sqrt{4.5}}{3 \times 10^8 \text{ m/s}} = 898 \text{ ps}$

$v = \frac{c}{\sqrt{\varepsilon_r}} = \frac{3 \times 10^8 \text{ m/s}}{\sqrt{4.5}} = 1.41 \times 10^8 \text{ m/s}$

If the transmission line is a microstrip, the same procedure is used to calculate the velocity, but with the effective dielectric constant as calculated in equation (2.6).

Since  $Z_o = \sqrt{L/C}$  and  $TD = \sqrt{LC}$ , we have two equations and two unknowns. Solve for L and C

$$L_{\text{total}} = (\text{TD})(Z_o) = (898 \times 10^{-12})(50 \ \Omega) = 44.9 \text{ nH}$$

$$C_{\text{total}} = \frac{\text{TD}}{Z_o} = \frac{898 \times 10^{-12} \text{ s}}{50 \ \Omega} = 17.9 \text{ pF}$$

The L and C values above are the total inductance and capacitance for the 5-in. line.

segments

$$\geq 10 \left( \frac{X}{T_r v} \right) = 10 \left[ \frac{5 \text{ in.}(0.0254 m/\text{in.})}{2.5 \text{ ns}(1.41 \times 10^8 m/\text{s})} \right] = 3.6$$

Because 3.6 is not a round number, we will use four segments in the model.

$$C_{\text{segment}} = \frac{C_{\text{total}}}{\text{segments}} = \frac{17.9 \text{ pF}}{4} = 4.48 \text{ pF}$$

$$L_{\text{segment}} = \frac{L_{\text{total}}}{\text{segments}} = \frac{44.9 \text{ nH}}{4} = 11.23 \text{ nH}$$

The final loss-free transmission line equivalent circuit is shown in Figure 2.7b.

Double check to ensure that the rule of thumb is satisfied.

$$TD_{segment} = \sqrt{L_{segment}C_{segment}} = \sqrt{(4.48 \text{ pF})(11.23 \text{ nH})} = 0.224 \text{ ns} \le \frac{T_r}{10}$$

# 2.4. LAUNCHING INITIAL WAVE AND TRANSMISSION LINE REFLECTIONS

The characteristics of the driving circuitry and the transmission line greatly affect the integrity of a signal being transmitted from one device to another. Subsequently, it is very important to understand how the signal is launched onto a transmission line and how it will look at the receiver. Although many parameters will affect the integrity of the signal at the receiver, in this section we describe the most basic behavior.

#### 2.4.1. Initial Wave

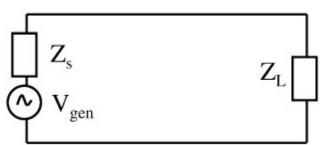

When a driver launches a signal onto a transmission line, the magnitude of the signal depends on the voltage and source resistance of the buffer and the impedance of the transmission line. The initial voltage seen at the driver will be governed by the voltage divider of the source resistance and the line impedance. Figure 2.8 depicts an initial wave being launched onto a long transmission line. The initial voltage  $V_i$  will propagate down the transmission line until it reaches the end. The magnitude of  $V_i$  is determined by the voltage divider between the source and the line impedance:

$$(2.8) V_i = V_s \frac{Z_o}{Z_o + Z_s}$$

Figure 2.8: Launching a wave onto a long transmission line.

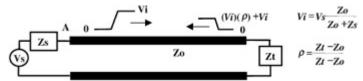

If the end of the transmission line is terminated with an impedance that exactly matches the characteristic impedance of the line, the signal with amplitude  $V_i$  will be terminated to ground and the voltage  $V_i$  will remain on the line until the signal source switches again. In this case the voltage  $V_i$  is the dc steady-state value. Otherwise, if the end of the transmission line exhibits some impedance other than the characteristic impedance of the line, a portion of the signal will be terminated to ground and the remainder of the signal will be reflected back down the transmission line toward the source. The amount of signal reflected back is determined by the *reflection coefficient*, defined as the ratio of the reflected voltage to the incident voltage seen at a given junction. In this context, a *junction* is defined as an impedance discontinuity on a transmission line. The impedance discontinuity could be a section of transmission line with different characteristic impedance, a terminating resistor, or the input impedance to a buffer on a chip. The reflection coefficient is calculated as

(2.9)

$$\rho = \frac{V_{\text{reflected}}}{V_{\text{incident}}} = \frac{Z_t - Z_o}{Z_t + Z_o}$$

impedance of the line, and  $Z_t$  the impedance of the discontinuity. The equation assumes that the signal is traveling on a transmission line with characteristic impedance  $Z_o$  and encounters an impedance discontinuity of  $Z_t$ . Note that if  $Z_o = Z_t$ , the reflection coefficient is zero, meaning that there is no reflection. The case where  $Z_o = Z_t$  is known as *matched termination*.

As depicted in Figure 2.9, when the incident wave hits the termination  $Z_t$ , a portion of the signal,  $V_{ip}$ , is reflected back toward the source and is added to the incident wave to produce

a total magnitude on the line of  $V_{i\rho}$  +  $V_i$ . The reflected component will then travel back to the source and possibly generate another reflection off the source. This reflection and counterreflection continues until the line has reached a stable condition.

Figure 2.9: Incident signal being reflected from an unmatched load.

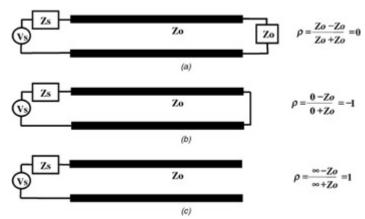

<u>Figure 2.10</u> depicts special cases of the reflection coefficient. When the line is terminated in a value that is exactly equal to its characteristic impedance, there is no discontinuity, and the signal is terminated to ground with no reflections. With open and shorted loads, the reflection is 100%, however, the reflected signal is positive and negative, respectively.

**Figure 2.10:** Reflection coefficient for special cases: (a) terminated in  $Z_0$ ; (b) short circuit; (c) open circuit.

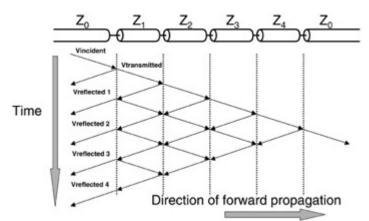

## 2.4.2. Multiple Reflections

As described above, when a signal is reflected from an impedance discontinuity at the end of the line, a portion of the signal will be reflected back toward the source. When the reflected signal reaches the source, another reflection will be generated if the source impedance does not equal that of the transmission line. Subsequently, if an impedance discontinuity exists on both sides of the transmission line, the signal will bounce back and forth between the driver and receiver. The signal reflections will eventually reach steady state at the dc solution.

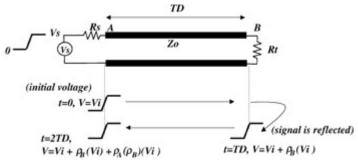

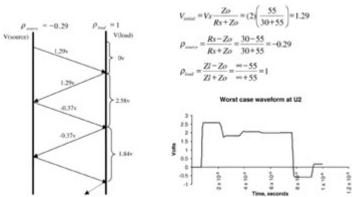

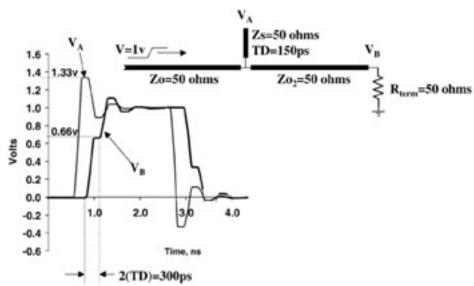

For example, consider Figure 2.11, which shows one example for a time interval of a few TD (where TD is the time delay of the transmission line from source to load). When the source transitions to  $V_s$ , the initial voltage on the line,  $V_i$ , is determined by the voltage divider  $V_i = V_s Z_o / (Z_o + R_s)$ . At time t = TD, the incident voltage  $V_i$  arrives at the load  $R_t$ . At this time a reflected component is generated with a magnitude of  $\rho_B V_i$ , which is added to the incident voltage  $V_i$ , creating a total voltage at the load of  $V_i + \rho_B V_i$  ( $\rho_B$  is the reflection coefficient looking into the load). The reflected portion of the wave ( $\rho_B V_i$ ) then travels back to the source and at time t = 2TD generates a reflection off the source determined by  $\rho_A \rho_B V_i$  ( $\rho_A$  is the reflection coefficient looking into the source). At this time the voltage seen at the source will be the previous voltage ( $V_i$ ) plus the incident transient voltage from the reflection ( $\rho_B V_i$ ) plus the reflected wave ( $\rho_A \rho_B V_i$ ). This reflecting and counter-reflecting will continue until the line voltage has approached the steady-state dc value. As the reader can see, the reflections

could take a long time to settle out if the termination is not matched and can have some significant timing impacts.

Figure 2.11: Example of transmission line with reflections.

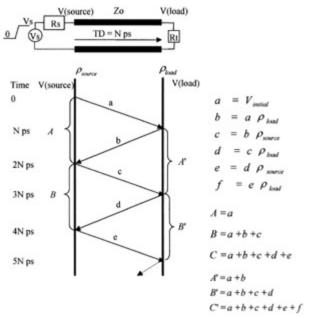

It is apparent that hand calculation of multiple reflections can be rather tedious. An easier way to predict the effect of reflections on a signal is to use a lattice diagram.

#### Lattice Diagrams and Over-and Underdriven Transmission Lines.

A lattice diagram (sometimes called a bounce diagram) is a technique used to solve the multiple reflections on a transmission line with linear loads. Figure 2.12 shows a sample lattice diagram. The left-and right-hand vertical lines represent the source and load ends of the transmission line. The diagonal lines contained between the vertical lines represent the signal bouncing back and forth between the source and the load. The diagram progressing from top to bottom represents increasing time. Notice that the time increment is equal to the time delay of the transmission line. Also note that the vertical bars are labeled with reflection coefficients at the top of the diagram. These reflection coefficients represent the reflection between the transmission line and the load (looking into the load from the line) and the reflection coefficient looking into the source. The lowercase letters represent the magnitude of the reflected signal traveling on the line, the uppercase letters represent the voltages seen at the source, and the primed uppercase letters represent the voltage seen at the load end of the line. For example, referring to Figure 2.12, the near end of the line will be held at a voltage of A volts for a duration of 2N picoseconds, where N is the time delay (TD) of the transmission line. The voltage A is simply the initial voltage  $V_{\text{initial}}$ , which will remain constant until the reflection from the load reaches the source. The voltage A' is simply the voltage a plus the reflected voltage b. The voltage B is the sum of the incident voltage a, the signal reflected from the load b, the signal reflected off the source c, and so on. The reflections on the line eventually reach the steady-state voltage of the source,  $V_s$ , if the line is open. However, if the line is terminated with a resistor,  $R_t$ , the steady-state voltage is computed as

$$(2.10) V_s \frac{R_t}{R_t + R_s}$$

Figure 2.12: Lattice diagram used to calculate multiple reflections on a transmission line.

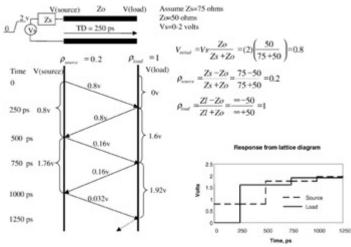

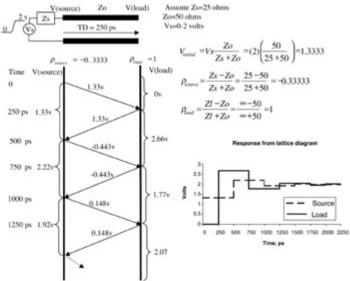

#### **Example 2.2: Multiple Reflections for an Underdriven Transmission Line.**

As described above, when the driver launches a signal onto the transmission line, the initial voltage present on the transmission line will be governed by the voltage divider between the driver impedance  $Z_s$  and the line impedance  $Z_o$ . As shown in Figure 2.13, this value is 0.8 V. The initial signal, 0.8 V, will travel down the line until it reaches the load. In this particular case, the load is open and thus has a reflection coefficient of 1. Subsequently, the entire signal is reflected back toward the source and is added to the incident signal of 0.8 V. So at time = TD, 250 ps in this example, the signal seen at the load is 0.8 + 0.8, or 1.6 V. The 0.8-V reflected signal will then propagate down the line toward the source. When the signal reaches the source, part of the signal will be reflected back toward the load. The magnitude of the reflected signal depends on the reflection coefficient between the line impedance  $Z_o$  and the source impedance  $Z_s$ . In this example the value reflected toward the load is (0.8 V)(0.2), which is 0.16 V. The reflected signal will be added to the signal already present on the line, which will give a total magnitude of 1.76 V, with the reflected portion of 0.16 V traveling to the load. This process is repeated until the voltage reaches a steady-state value of 2 V.

**Figure 2.13:** Example 2.2: Lattice diagram used to calculate multiple reflections for an underdriven transmission line.

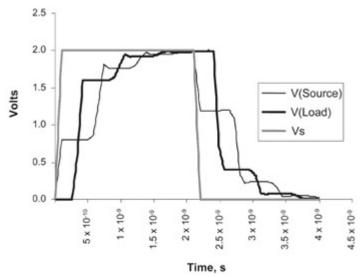

The response of the lattice diagram is shown in the lower corner of <u>Figure 2.13</u>. A computer simulation of the response is shown in <u>Figure 2.14</u> for comparison. Notice how the reflections give the waveform a "stair-step" appearance at the receiver, even though the unloaded output of the voltage source is a square wave. This effect occurs when the source impedance  $Z_s$  is larger than the line impedance  $Z_o$  and is referred to as an *underdriven transmission line*.

**Figure 2.14:** Simulation of transmission line system shown in <u>Example 2.2</u>, where the line impedance is less than the source impedance (underdriven transmission line).

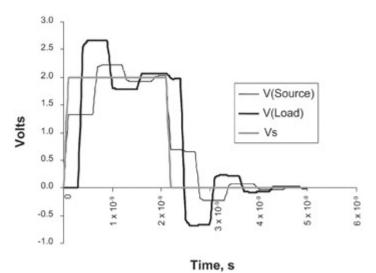

**Example 2.3: Multiple Reflections for an Overdriven Transmission Line.**

When the line impedance is greater than the source impedance, the reflection coefficient looking into the source will be negative, which will produce a "ringing" effect. This is known as an *overdriven transmission line*. The lattice diagram for an overdriven transmission line is shown in <u>Figure 2.15</u>. <u>Figure 2.16</u> is a SPICE simulation showing the response of the system depicted in <u>Figure 2.15</u>.

**Figure 2.15:** Example 2.3: Lattice diagram used to calculate multiple reflections for an overdriven transmission line.

**Figure 2.16:** Simulation of transmission line system shown in <u>Example 2.3</u> where the line impedance is greater than the source impedance (over-driven transmission line).

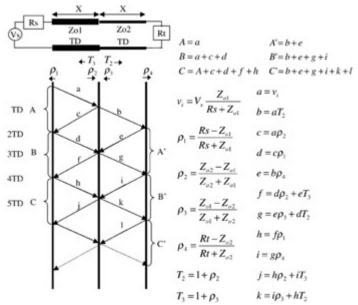

Next, consider the transmission line structure depicted in Figure 2.17. The structure consists of two segments of transmission line cascaded in series. The first section is of length X and has a characteristic impedance of  $Z_{o1}$  ohms. The second section is also of length X and has an impedance of  $Z_{o2}$  ohms. Finally, the structure is terminated with a value of  $R_t$ . When the signal encounters the  $Z_{o1}/Z_{o2}$  impedance junction, part of the signal will be reflected, as governed by the reflection coefficient, and part of the signal will be transmitted, as governed by the transmission coefficient:

$$^{(2.11)} T = 1 + \rho$$

Figure 2.17: Lattice diagram of transmission line system with multiple line impedances.

Figure 2.17 also depicts how a lattice diagram can be used to solve for multiple reflections on a transmission line system with more than one characteristic impedance. Note that the transmission lines in this example are of equal length, which simplifies the problem because the reflections on each section will be in phase. For example, refer to Figure 2.17 and note that the reflection, e, adds directly to the reflection, f. When the two transmission lines are of different lengths, the reflections from one section will not be in phase with the reflections from the other section, which complicates the diagram drastically. Once the system complexity progresses beyond the point depicted in Figure 2.17, it is preferable to use a simulator such as SPICE to solve the system.

#### Bergeron Diagrams and Reflections from Nonlinear Loads.

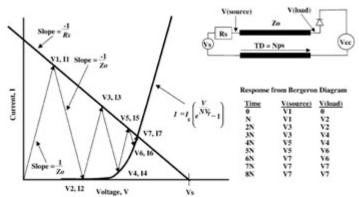

The *Bergeron diagram*.is another technique used for solving multiple reflections on a transmission line. A Bergeron diagram is used in place of a lattice diagram when nonlinear loads and sources exist in the system. A good example of when a Bergeron diagram is necessary is when a transmission line is terminated with a clamping diode to prevent excess signal overshoot or damage due to electrostatic discharge. Furthermore, output buffers rarely exhibit perfectly linear *I-V* characteristics; thus a Bergeron diagram will give a more accurate representation of the reflections if the *I-V* characteristics of the buffers are well known.

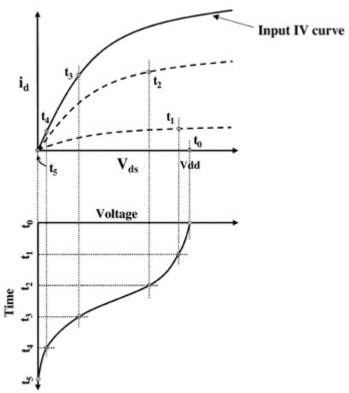

Refer to Figure 2.18. To construct a Bergeron diagram, plot the I-V characteristics of the load and the source. The source I-V curve will have a negative slope of  $1/R_s$  since current is leaving the node and the X intercept will be at  $V_s$ . Then, beginning with the transmission line's initial condition (i.e., V = 0, I = 0), construct a line with a slope of  $1/Z_o$ . The point where this line intersects the source I-V curve gives the initial voltage and current on the line at the source at time = 0. You may recognize this as a load diagram. From the intersection with the

source line, construct a line with a slope of  $-1/Z_o$  and extend the line to the load curve. This vector represents the signal traveling down the line toward the load. The intersection with the load line will define the voltage and current at the load at time = TD, where TD is the time delay of the line. Repeat this procedure using alternating slopes of  $1/Z_o$  and  $-1/Z_o$  until the transmission line vectors reach the point where the load and source lines intersect. The intersections of the transmission line vectors and the load and source I-V curves give the voltage and current values at steady state. Figure 2.19 is an example that calculates the response of a similar system where  $V_s = 3$  V, TD = 500 ps,  $Z_o = 50$   $\Omega$ ,  $R_s = 25$   $\Omega$ , and the diode behaves with the equation shown.

Figure 2.18: Bergeron diagram used to calculate multiple reflection with a nonlinear load.

**Figure 2.19:** Bergeron diagram used to calculate the reflection on a transmission line with a diode termination.

#### **POINT TO REMEMBER**

Use a Bergeron diagram to calculate the reflections on a transmission line when either the source or load exhibits significant nonlinear *I-V* characteristics.

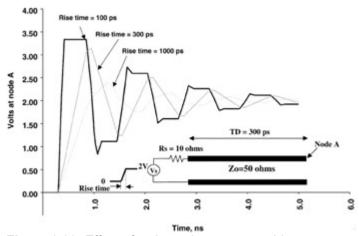

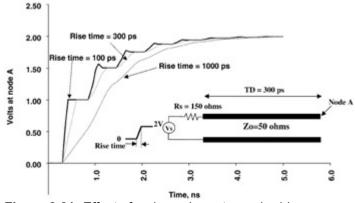

#### 2.4.3. Effect of Rise Time on Reflections

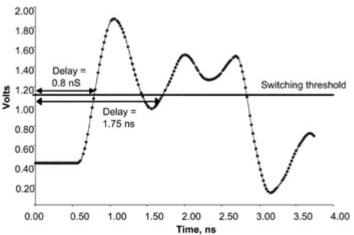

The rise time will begin to have a significant effect on the wave shape when it becomes less than twice the delay (TD) of the transmission line. <u>Figures 2.20</u> and <u>2.21</u> show the effect that edge rate has on underdriven and overdriven transmission lines. Notice how significantly the wave shape changes as the rise time exceeds twice the delay of the line. When the edge rate exceeds twice the line delay, the reflection from the source arrives before the transition from one state to another is complete (i.e., high-to-low or low-to-high transition).

Figure 2.20: Effect of a slow edge rate: overdriven case.

Figure 2.21: Effect of a slow edge rate: underdriven case.

#### 2.4.4. Reflections from Reactive Loads

In real systems there are rarely cases where the loads are purely resistive. The input to a CMOS gate, for example, tends to be capacitive. Additionally, bond wires and the lead

frames of the chip packages are quite inductive. This makes it necessary to understand how these reactive elements affect the reflections in a system. In this section we introduce the effect that capacitors and inductors have on reflections. This knowledge will be used as a basis in future chapters, where capacitive and inductive parasitic effects are explored in more detail.

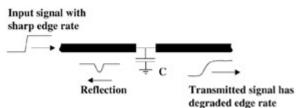

#### Reflections from a Capacitive Load.

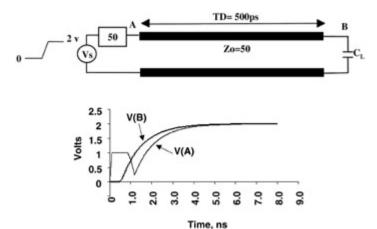

When a transmission line is terminated in a reactive element such as a capacitor, the waveforms at the driver and load will have a shape quite different from that of the typical transmission line response. Essentially, a capacitor is a time-dependent load, which will initially look like a short circuit when the signal reaches the capacitor and will look like an open circuit after the capacitor is fully charged. Let's consider the reflection coefficient at time = TD and at time =  $t_1$ . At time = TD, which is the time when the signal has propagated down the line and has reached the capacitive load, the capacitor will not be charged and will look like a short circuit. As described earlier in the chapter, a short circuit will have a reflection coefficient of -1. This means that the initial wave of magnitude V will be reflected off the load with a magnitude of -V, yielding an initial voltage of 0 V. The capacitor will then begin to charge at a rate dependent on  $\tau$ , which is the time constant of an RC circuit, where C is the termination capacitor and R is the characteristic impedance of the transmission line. Once the capacitor is fully charged, the reflection coefficient will be 1 since the capacitor will resemble an open circuit. The voltage at the capacitor beginning at time t = t = t = t = t = t = t = t = t = t = t = t = t = t = t = t = t = t = t = t = t = t = t = t = t = t = t = t = t = t = t = t = t = t = t = t = t = t = t = t = t = t = t = t = t = t = t = t = t = t = t = t = t = t = t = t = t = t = t = t = t = t = t = t = t = t = t = t = t = t = t = t = t = t = t = t = t = t = t = t = t = t = t = t = t = t = t = t = t = t = t = t = t = t = t = t = t = t = t = t = t = t = t = t = t = t = t = t = t = t = t = t = t = t = t = t = t = t = t = t = t = t = t =

(2.12)

$$V_{\text{capacitor}} = 2V_i(1 - e^{-(t-\text{TD})/\tau}), \qquad t > \text{TD}$$

(2.13)  $\tau = CZ_o$

Figure 2.22 shows a simulation of the response of a line terminated with a capacitive load. The load capacitance is 10 pF, the line length is 3.5 in. (TD = 500 ps), and the driver and transmission line impedance are both 50  $\Omega$ . Notice the shape of the waveform at the source (node A). It dips toward 0 at 1 ns, which is 2TD, the time that the reflection from the load arrives at the source. It dips toward zero because the initial reflection coefficient off the capacitor is -1, so the voltage reflected back toward the source is initially  $V_i + (-V_i)$ , where  $V_i$  is the initial voltage launched onto the transmission line. The capacitor then charges to a steady-state value of 2 V.

Figure 2.22: Transmission line terminated in a capacitive load.

If the line is terminated with a parallel resistor and capacitor, as depicted in <u>Figure 2.23</u>, the voltage at the capacitor will depend on

(2.14)

$$V_{\text{capacitor}} = 2V_i \frac{R_L}{R_L + Z_o} (1 - e^{-(t-\text{TD})/\tau_1}), \quad t > \text{TD}$$

and the time constant will depend on the  $C_L$  and the parallel combination of  $R_L$  and  $Z_o$ :

(2.15)

$$\tau_1 = \frac{C_L Z_o R_L}{R_L + Z_o}$$

Figure 2.23: Transmission line terminated in a parallel capacitive and resistive load.

#### Reflection from an Inductive Load.

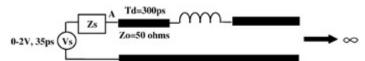

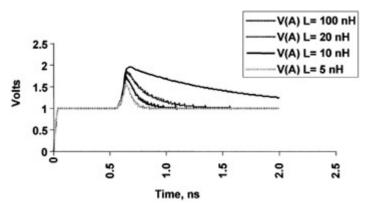

When a series inductor appears in the electrical pathway on a transmission line, as depicted in Figure 2.24, it will also act as a time-dependent load. Initially, at time = 0, the inductor will resemble on open circuit. When a voltage step is applied initially, almost no current flows across the inductor. This produces a reflection coefficient of 1. The value of the inductor will determine how long the reflection coefficient will remain 1. If the inductor is large enough, the signal will double in magnitude. Eventually, the inductor will discharge its energy at a rate that depends on the time constant  $\tau$  of an LR circuit, which will have a value of  $L/Z_o$ . Figure 2.25 shows the reflections from four different values of the series inductor depicted in Figure 2.24. Notice that the magnitude of the reflection and the decay time increased with increasing inductor value.

Figure 2.24: Series inductor.

Figure 2.25: Reflection as seen at node A of Figure 2.24 for different inductor values.

#### 2.4.5. Termination Schemes to Eliminate Reflections

As explained in later chapters, reflections on a transmission line can have a significant negative impact on the performance of a digital system. To minimize the negative impact of the reflections, methods must be developed to control them. Essentially, there are three ways to mitigate the negative impact of these reflections. The first method is to decrease the frequency of the system so that the reflections on the transmission line reach steady state before another signal is driven onto the line. This is usually impossible, however, for high-speed systems since it requires decreasing the operating frequency, producing a low-speed system. The second method is to shorten the PCB traces so that the reflections will reach steady state in a shorter time. This is usually not practical since doing so generally involves using a PCB board with a greater number of layers, which increases cost significantly. Additionally, shortening the traces may be physically impossible in some cases. These first two methods always have a limit at which the bus frequency increases to a point where the reflections won't reach steady state in one period. The third method is to terminate the transmission line with an impedance equal to the characteristic impedance of the line at either end of the transmission line and eliminate the reflections.

When the source end of the transmission line is designed to match the characteristic impedance of the transmission line, the bus is said to be *source terminated*. When a bus is source terminated, any reflections produced by a large impedance discontinuity at the far end of the line (such as an open circuit) are eliminated when they reach the source because the reflection coefficient will be zero. When a terminating resistor is placed at the far end of the line, the bus is said to be *parallel*, or *load terminated*. Multiple reflections will be eliminated at the load because the reflection coefficient at the load is zero. There are several different ways to implement these termination methodologies. There are advantages and disadvantages to each technique. Several techniques are summarized in the following sections.

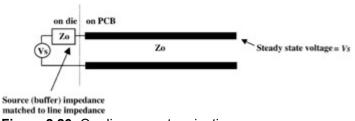

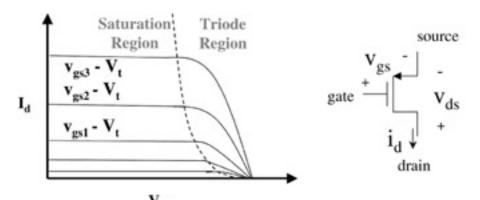

#### On-Die Source Termination.

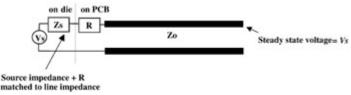

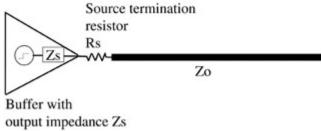

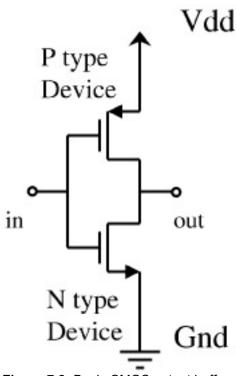

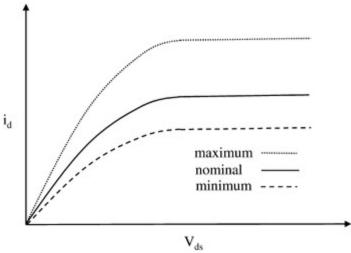

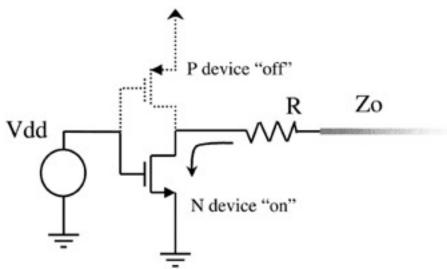

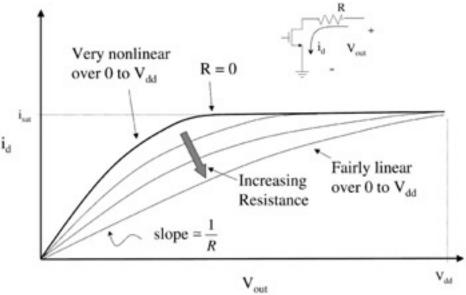

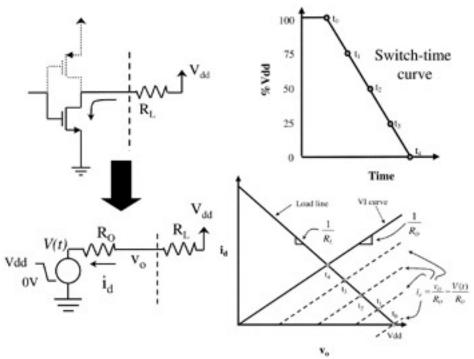

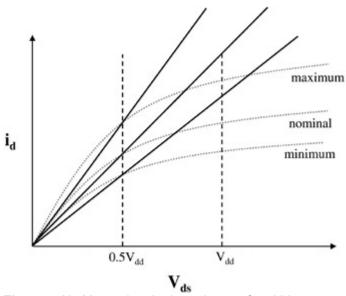

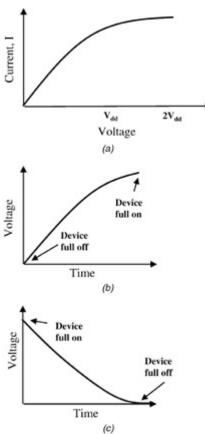

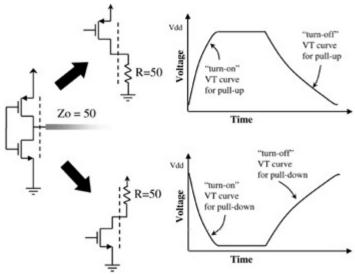

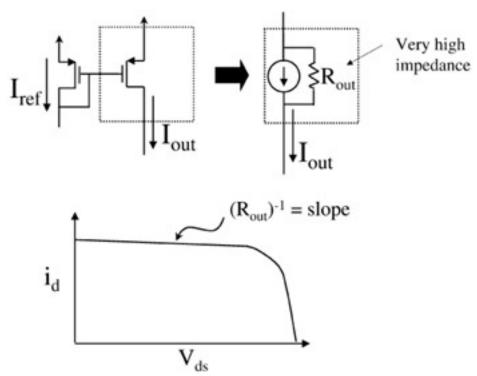

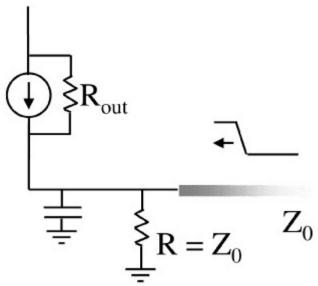

On-die source termination requires that the *I-V* curve of the output buffer be very linear over the operating range and yield an *I-V* curve with an impedance very close to the transmission line impedance. Ideally, this is an optimum solution because it does not require any additional components that increase cost and consume area on the board. However, since there are numerous variables that drastically affect the output impedance of a buffer, it is difficult to achieve a good match between the buffer impedance and the line impedance. Some of the variables that affect the buffer impedance are silicon fabrication process variations, voltage, temperature, power delivery factors, and simultaneous switching noise. These variations will make it difficult to guarantee that the buffer impedance will match the line impedance. Figure 2.26 depicts this termination method.

Figure 2.26: On-die source termination.

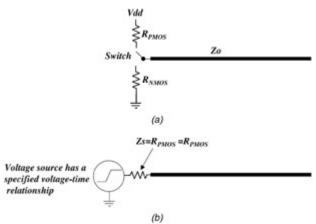

#### **Series Source Termination.**

Series source termination requires that a resistor be added in series with the output buffer. Figure 2.27 depicts the implementation of a series source termination. This type of termination requires that the sum of the buffer impedance and the value of the resistor be

equal to the characteristic impedance of the line. This is usually best achieved by designing the *I-V* curve of the output buffer to yield a very low impedance such that the bulk of the impedance looking into the source will be contained in the resistor. Since precision resistors can be chosen, the effect of the on-die impedance variation due to process and environmental variations on the silicon that make on-die source termination difficult can be minimized. The total variation in impedance will be small because the resistor, rather than the output buffer itself, will comprise the bulk of the impedance. The disadvantages of this technique are that the resistors add cost to the board, and it consumes significant board area.

Figure 2.27: Series source termination.

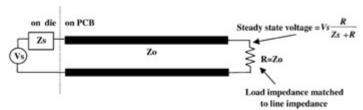

#### Load Termination with a Resistive Load.

Load or parallel termination with a resistive load eliminates the unknown variables associated with the buffer impedance because a precision resistor can be used. The reflections are eliminated at the load and low-impedance output buffers may be used. The disadvantage is that a large portion of the dc current will be shunted to ground, which exacerbates power delivery and thermal problems. The steady-state voltage will also be determined from the voltage divider between the source resistance and the load resistance, which creates the need for stronger buffers. Power delivery is a difficult problem to solve in modern computers. Laptops, for example, need very efficient power delivery systems since they require the use of batteries over prolonged periods of time. As power consumption increases, cost also increases, because more elaborate cooling mechanisms must be introduced to dissipate the excess heat. Figure 2.28 depicts this termination scheme.

Figure 2.28: Load termination.

#### AC Load Termination.

Ac load termination uses a series capacitor and resistor at the load end of a transmission line to eliminate the reflections. The resistor R should be equal to the characteristic impedance of the transmission line, and the capacitor  $C_L$  should be chosen such that the RC time constant at the load is approximately equal to one or two rise times. It is advised that simulations be performed to choose the optimum capacitor value for the specific design. The premise behind this termination scheme is that the capacitor will initially act like a short circuit and the line will be terminated in its characteristic impedance by the resistor R for the duration of the rising or falling edge. The capacitor will then charge up and the steady-state voltage of the source,  $V_s$ , will be reached. The advantage of this technique is that the reflections are eliminated at the load with no dc power dissipation. The disadvantages are that the capacitive loading will increase the signal delay by slowing down the rising or falling

times at the load. Furthermore, the additional resistors and capacitors consume board area and increase cost. Figure 2.29 depicts this termination scheme.

Figure 2.29: Ac load termination.

#### **Common Termination Problems.**

One of the common obstacles encountered during bus design is that the characteristic impedance of the trace tends to vary significantly, due to PCB production variations. The PCB variation affects all the termination methods; however, it tends to have a bigger impact on source termination. Typical, low-cost PCB boards, for example, usually vary as much as  $\pm 15\%$  from the target impedance over process. This means that if an engineer specifies a 65- $\Omega$  impedance for the lines on a PCB board, the vendor will guarantee that the impedance will be within 55.25  $\Omega$  (65  $\Omega$  - 15%) and 74.75  $\Omega$ (65  $\Omega$  + 15%). Finally, crosstalk will introduce additional variations in the impedance. The impact of the crosstalk-induced variations will depend on trace-to-trace spacing, the dielectric constant, and the cross-sectional geometry. Crosstalk is discussed thoroughly in Chapter 3.

For short lines, when the minimum digital pulse width is long compared to the time delay (TD) of the transmission line, source termination is desirable since it eliminates the need to shunt a portion of the driver current to ground. For long lines, where the width of the digital pulse is smaller than the time delay (TD) of the line, load termination is preferable. In the latter case, there will be multiple signals traveling down the transmission line at any given time (this is known as *pipeline mode*). Since reflections off the load will reflect back toward the source and interfere with the signals propagating down the line, the reflections must be eliminated at the load.

#### 2.5. ADDITIONAL EXAMPLES

#### 2.5.1. **Problem**

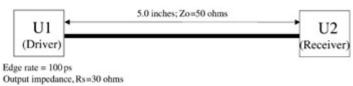

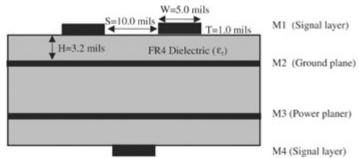

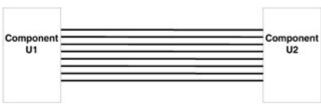

Assume that two components,  $U_1$  and  $U_2$ , need to communicate with each other via a high-speed digital bus. The components are mounted on a standard four-layer motherboard with the stackup shown in <u>Figure 2.30</u>. The driving buffers on component  $U_1$  have an impedance of 30  $\Omega$ , an edge rate of 100 ps, and a swing of 0 to 2 V. The traces on the PCB are required to be 50  $\Omega$  and 5 in. long. The relative dielectric constant of the board ( $\varepsilon_r$ ) is 4.0, the transmission line is assumed to be a perfect conductor, and the receiver capacitance is small enough to be ignored. <u>Figure 2.31</u> depicts the circuit topology.

Figure 2.30: Standard four layer motherboard stackup.

Figure 2.31: Topology of example circuits.

#### 2.5.2. Goals

- 1. Determine the correct cross-sectional geometry of the PCB shown in Figure 2.30 that will yield an impedance of 50  $\Omega$ .

- 2. Calculate the time it takes for the signal to travel from the driver, U<sub>1</sub>, to the receiver, U<sub>2</sub>.

- 3. Determine the wave shape seen at U<sub>2</sub> when the system is driven by U<sub>1</sub>.

- 4. Create an equivalent circuit of the system.

# 2.5.3. Calculating the Cross-Sectional Geometry of the PCB

Since the signal lines on the stackup depicted in Figure 2.30 are microstrips, the cross-sectional geometry can be determined from the equations in Figure 2.6. The fact that some of the microstrip lines are referencing a power plane instead of a ground plane should not cause confusion. For the purpose of transmission line design, a dc power plane will act like an ac ground and is treated as a ground plane in transmission line design. The consequences of this approximation are examined in subsequent chapters. Figure 2.6 shows that the trace impedance is a function of H, W, t, and  $\epsilon_r$  (see Figure 2.30):

$$Z_{o_{\text{microstrip}}} = \frac{87}{\sqrt{\varepsilon_r + 1.41}} \ln \frac{5.98H}{0.8W + t}$$

The standard metal thickness of microstrip layers on a PCB board is usually on the order of 1.0 mil. Since the desired impedance, dielectric constant  $\varepsilon_r$ , and the thickness are known, this leaves one equation and two unknowns. Subsequently, one value of either H or W needs to be chosen. Typical PCB manufacturers will usually deliver a minimum trace width of 5 mils. Since small trace widths use up less board real estate, which allows the PCB to be physically smaller and less expensive, the minimum trace width of 5.0 mils is chosen. Plugging the known values of  $\varepsilon_r$ , W, t, and t0 into the equation above and solving for t1 yields

$$50 = \frac{87}{\sqrt{4.0 + 1.41}} \ln \frac{5.98H}{0.8(5.0) + 1.0}$$

$$\frac{50\sqrt{5.41}}{87} = \ln \frac{5.98H}{5.0}$$

$$e^{1.337} = 1.196H$$

$$H = 3.2 \text{ mils}$$

Figure 2.32 depicts the resulting stackup of the PCB.

Figure 2.32: Resulting PCB stackup resulting in 50-ohm transmission lines.

Note the thickness of the inner metal and dielectric layers. The internal metal layers are only 0.7 mil thick instead of 1.0 mil thick. This is because the outer layers are usually tinplated to stop the outer copper traces, which are exposed to the environment, from oxidizing. The inner traces are not plated. Since a typical PCB board thickness requested by industry is 62 mils thick, the thickness of the dielectric layers between the power and ground plane is increased to achieve the desired board thickness.

# 2.5.4. Calculating the Propagation Delay

To calculate the time it takes for the signal to travel from  $U_1$  to  $U_2$ , it is necessary to determine the propagation velocity for a signal traveling on the transmission line that was just designed. Since the transmission line is a microstrip, the effective dielectric constant must be used to calculate the propagation velocity. The effective dielectric constant is calculated using equations (2.6) and (2.7).

$$\varepsilon_e = \frac{\varepsilon_r + 1}{2} + \frac{\varepsilon_r - 1}{2} \left( 1 + \frac{12H}{W} \right)^{-1/2} + F - 0.217(\varepsilon_r - 1) \frac{t}{\sqrt{WH}}$$

Since W/H = 5/3.2 > 1.0, then F = 0. Therefore,

$$\varepsilon_e = \frac{4.0 + 1}{2} + \frac{4.0 - 1}{2} \left[ 1 + \frac{12(3.2)}{5.0} \right]^{-1/2} + 0 - 0.217(4.0 - 1) \frac{1.0}{\sqrt{5.0(3.2)}}$$

= 2.84

The propagation velocity is determined using equation (2.2).

$$v = \frac{c}{\sqrt{\varepsilon_r}} = \frac{3.0 \times 10^8 \text{ m/s}}{\sqrt{2.84}} = 1.78 \times 10^8 \text{ m/s}$$

The time delay for the signal to propagate down the 5-in. line connecting  $U_1$  and  $U_2$  is then calculated using equation (2.4).

TD =

$$\frac{\text{length}\sqrt{\varepsilon_r}}{c} = \frac{5.0 \text{ in.}}{1.78 \text{ m/s}} \left(\frac{0.0254 \text{ m}}{1.0 \text{ in.}}\right) = 713 \text{ ps}$$

### 2.5.5. Determining the Wave Shape Seen at the Receiver

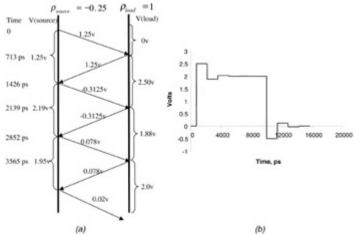

The easiest way to calculate the wave shape seen at the receiver is to use a lattice (or bounce) diagram (<u>Figure 2.33</u>). It should be noted that a Bergeron diagram could also be used; however, since there is no nonlinear device at the receiver such as a diode, the lattice diagram is the preferred method of analysis. Refer to Section 2.4.

**Figure 2.33:** Determining the wave shape at the receiver: (a) lattice diagram; (b) waveform at  $U_2$  when  $U_1$  is driving.

$$\begin{split} V_{\text{initial}} &= V_{\text{in}} \frac{Z_{o_{\text{PCB}}}}{Z_{o_{\text{PCB}}} + R_s} = 2.0 \left( \frac{50}{50 + 30} \right) = 1.25 \text{ V} \\ \rho_{\text{source}} &= \frac{R_s - Z_{o_{\text{PCB}}}}{R_s + Z_{o_{\text{PCB}}}} = \frac{30 - 50}{30 + 50} = -0.25 \\ \rho_{\text{load}} &= \frac{R_{\text{load}} - Z_{o_{\text{PCB}}}}{R_{\text{load}} + Z_{o_{\text{PCB}}}} = \frac{\infty - 50}{\infty + 50} = 1.0 \end{split}$$

where  $R_s$  is the buffer impedance of  $U_1$  and  $R_{load}$  is the open circuit seen at  $U_2$  (this assumes that the input capacitance to the buffer is very small, i.e., 2 to 3 pF).

### 2.5.6. Creating an Equivalent Circuit

To create the equivalent circuit model for this example, it is first necessary to determine the number of *LC* segments required. This is done using the rule of thumb presented in <u>Section 2.3.3</u>. To do so, it is convenient to convert the velocity calculated earlier to the units of inches/picosecond:

velocity (in/ps) =

$$\frac{5.0 \text{ in.}}{713 \text{ ps}} = 0.0070 \text{ in./ps}$$

segments  $\geq 10 \left( \frac{\text{length}}{T_r v} \right) = 10 \left[ \frac{5 \text{ in.}}{(100 \text{ ps})(0.0070 \text{ in./ps})} \right] = 71.4$

Therefore, the minimum of 72 segments is required to create an accurate transmission line model.

Now the equivalent inductance and capacitance per unit inch is calculated using <u>equations</u> (2.1) and (2.5). Since this particular example is loss-free (i.e., a perfect conductor is

assumed), equation (2.1) is reduced to  $Z_o = \sqrt{L/C}$ . The delay per unit inch is TD = 713 ps/5.0 in. = 142.6 ps/in. =  $\sqrt{LC}$ , where L and C are per unit inch.

The equivalent L and C per unit inch are calculated by solving TD and  $Z_0$  for L and C.

$$C = \frac{\text{TD}}{Z_o} = \frac{\sqrt{LC}}{\sqrt{L/C}} = \frac{142.6 \text{ ps}}{50} = 2.85 \text{ pF}$$

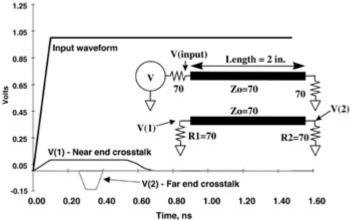

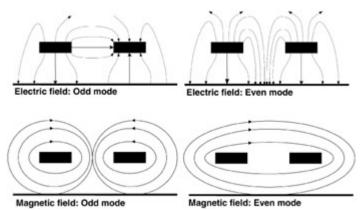

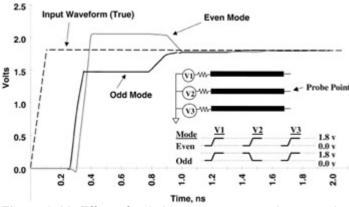

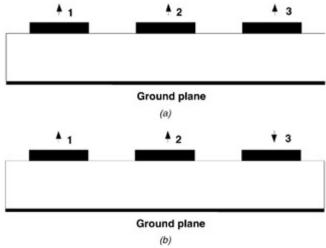

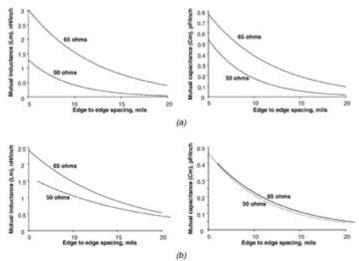

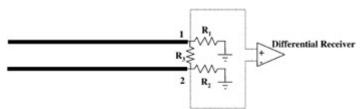

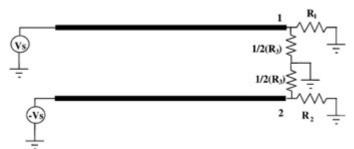

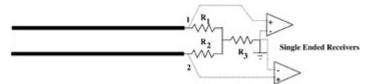

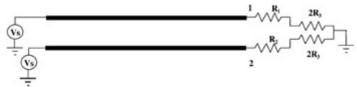

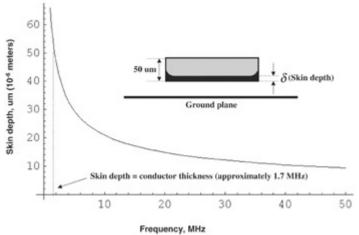

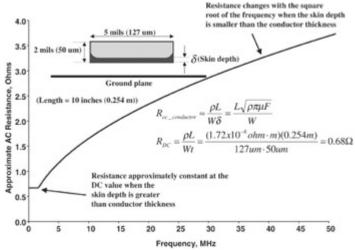

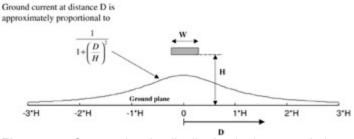

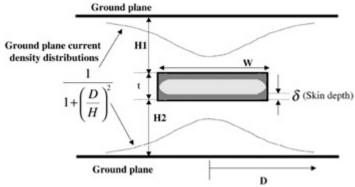

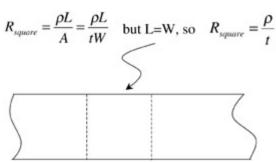

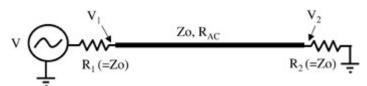

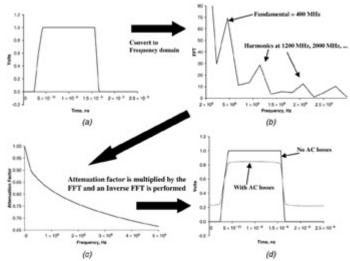

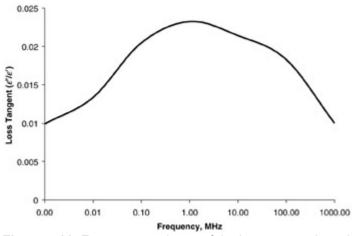

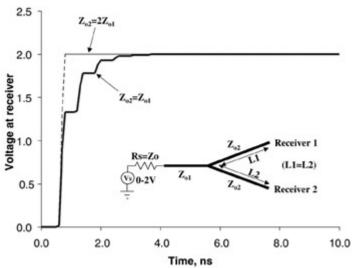

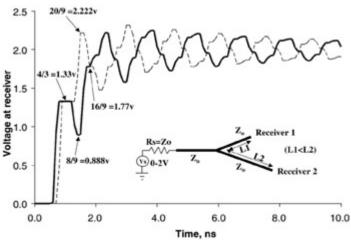

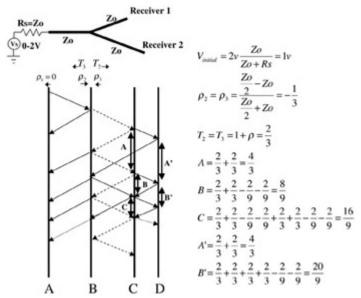

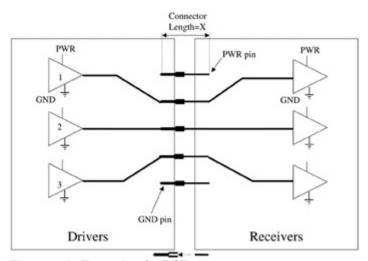

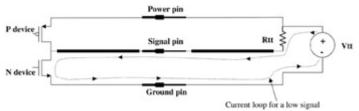

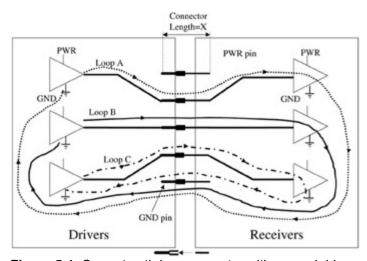

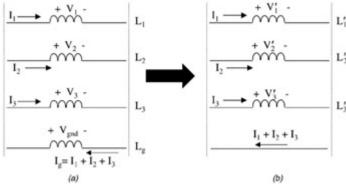

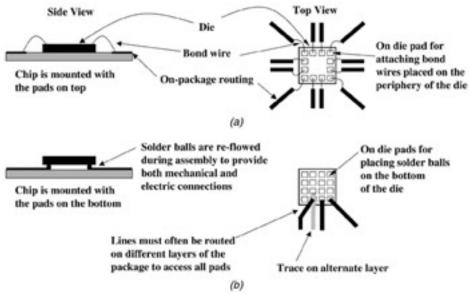

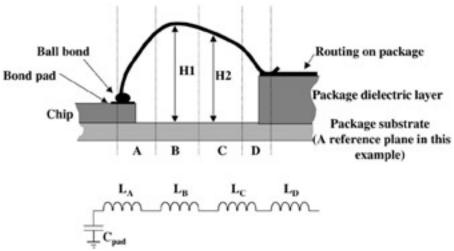

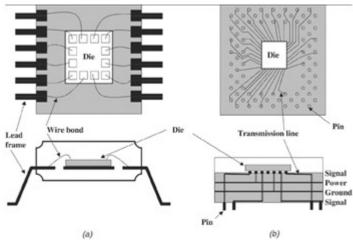

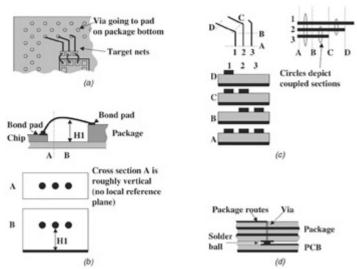

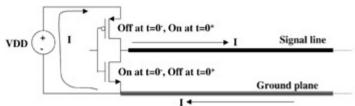

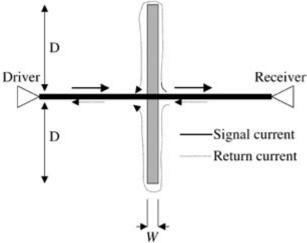

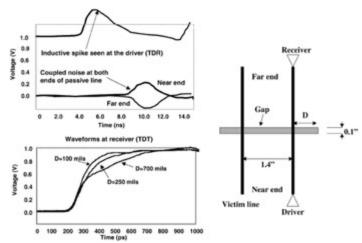

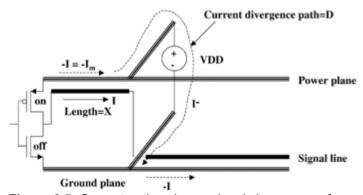

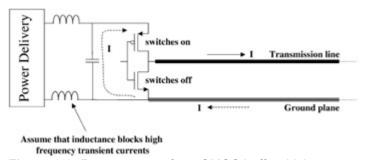

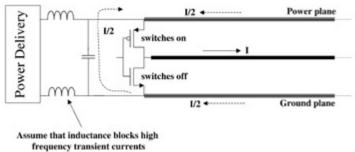

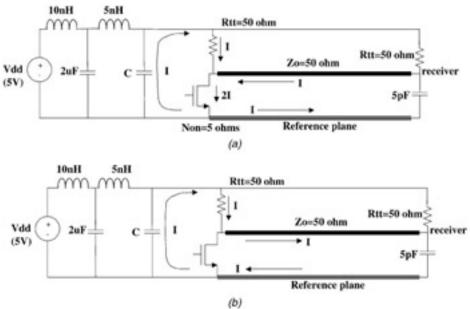

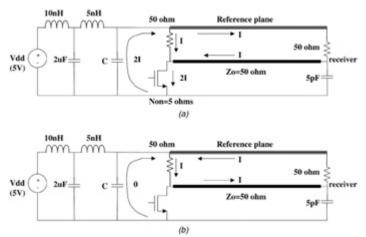

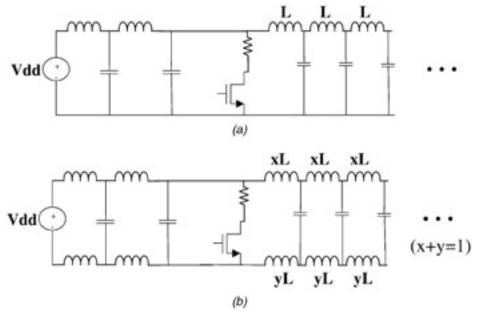

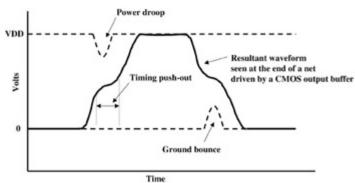

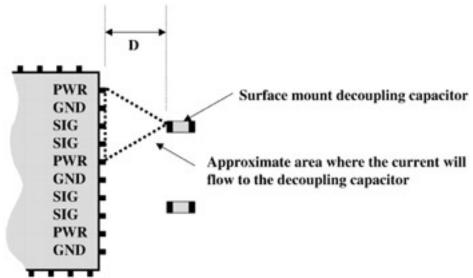

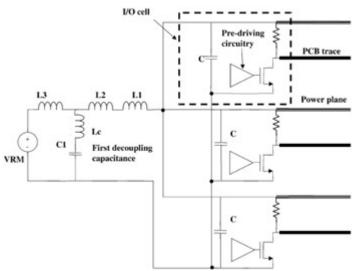

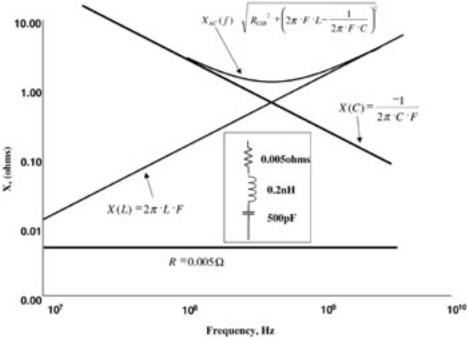

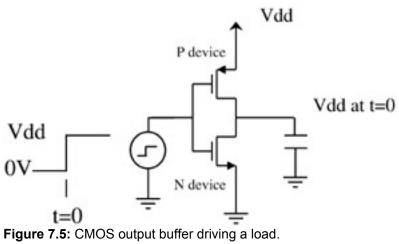

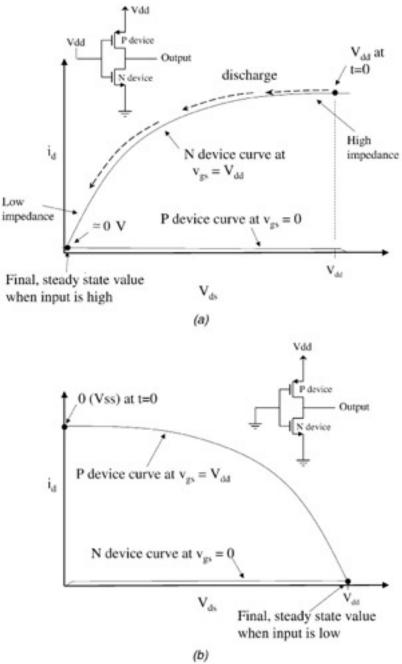

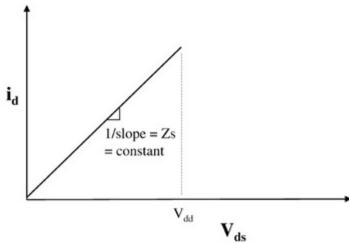

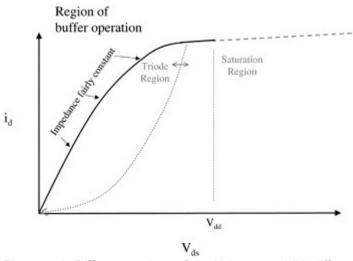

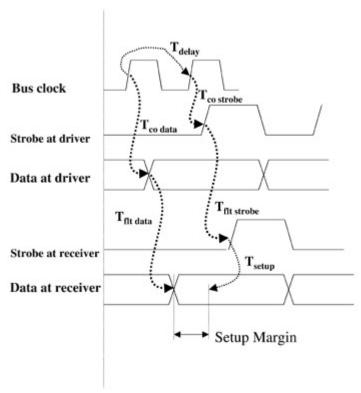

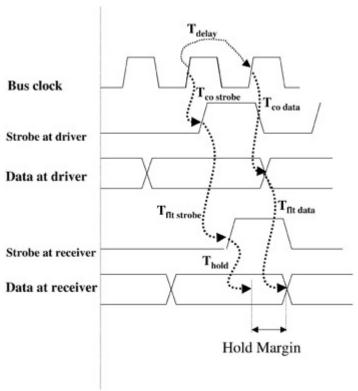

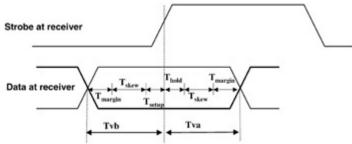

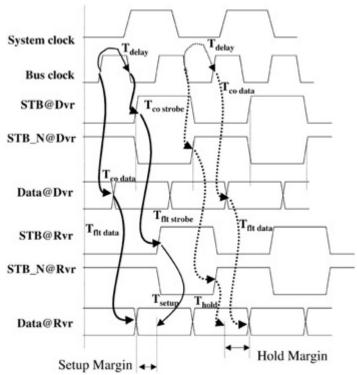

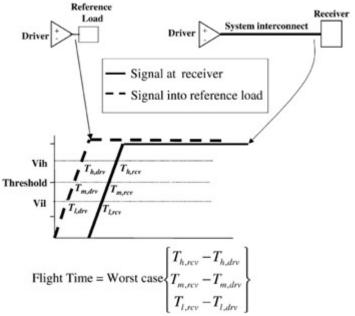

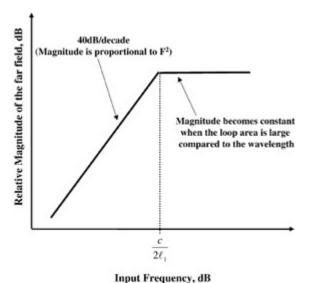

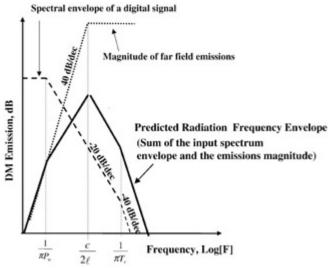

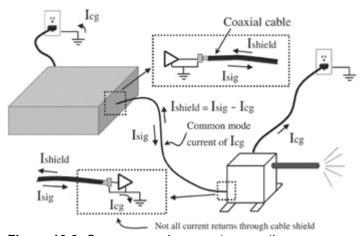

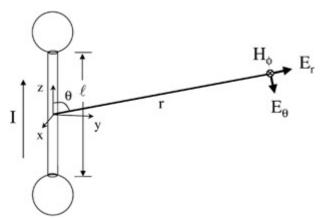

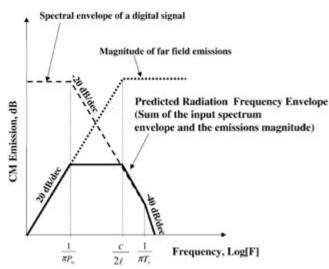

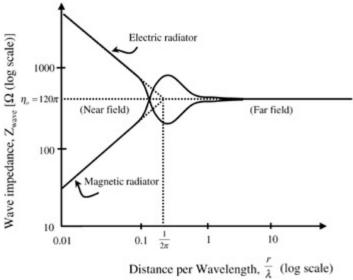

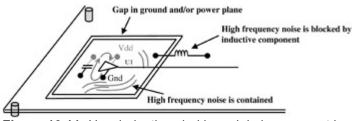

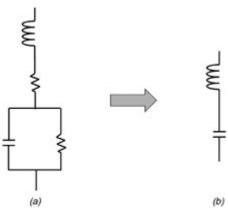

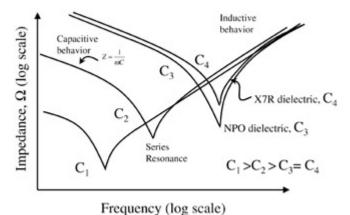

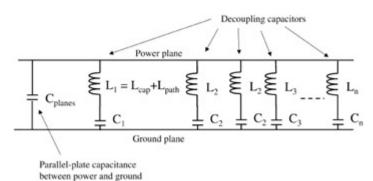

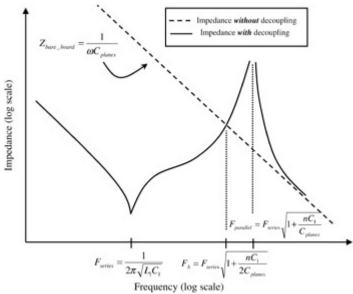

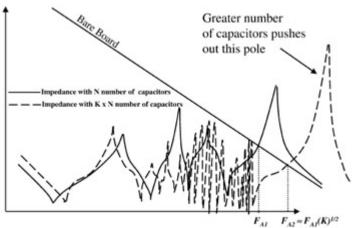

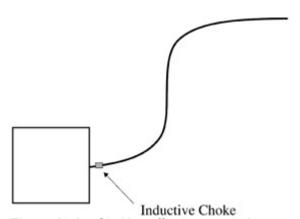

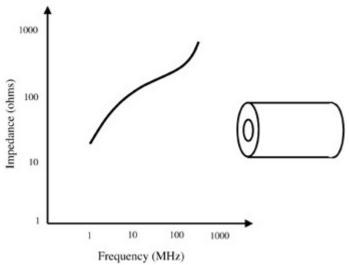

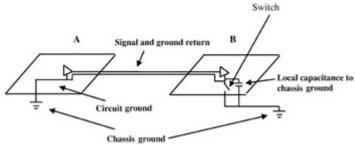

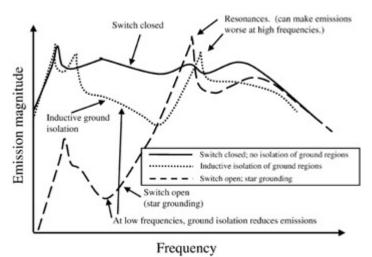

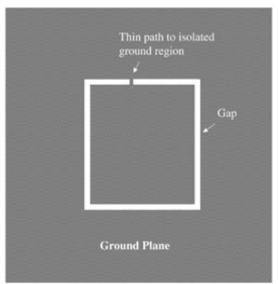

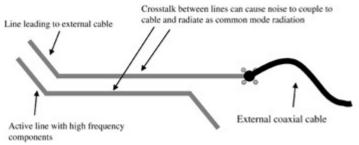

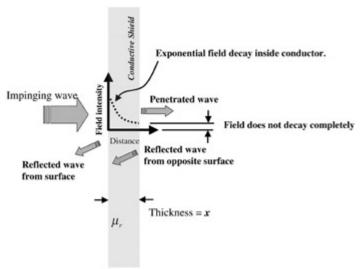

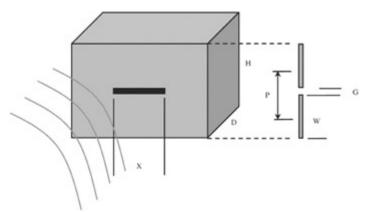

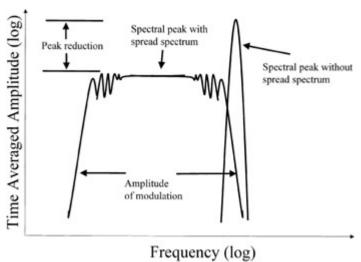

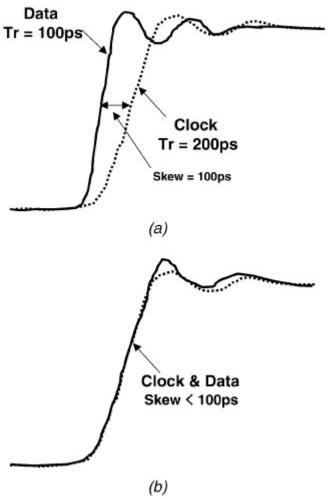

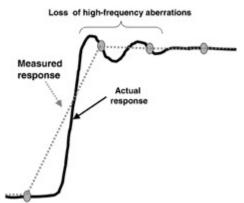

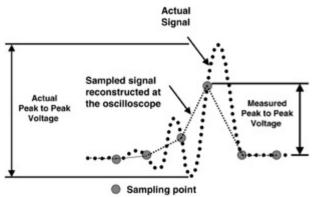

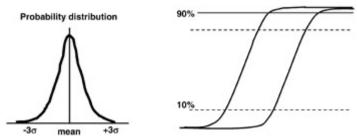

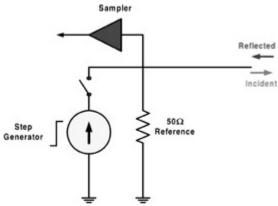

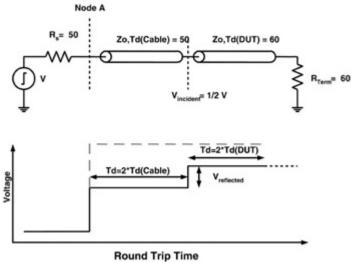

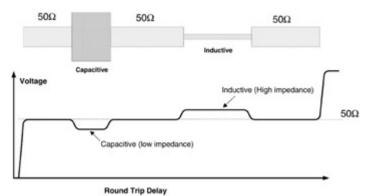

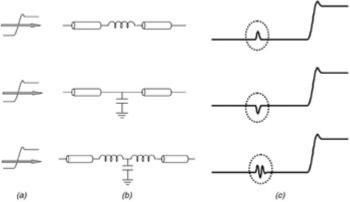

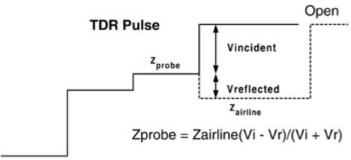

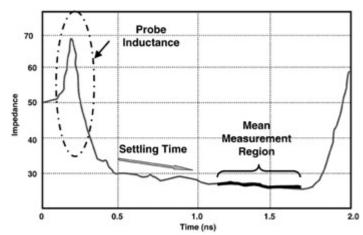

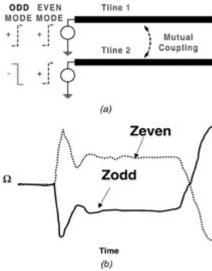

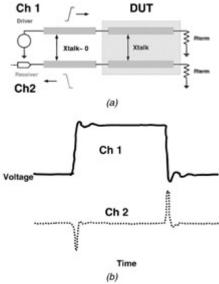

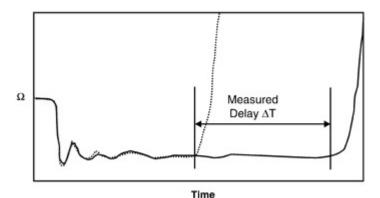

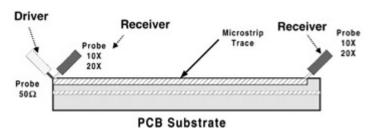

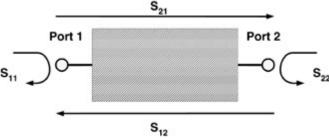

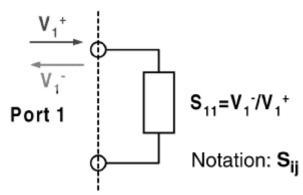

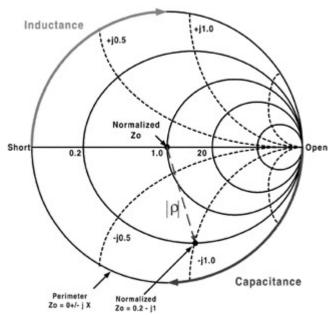

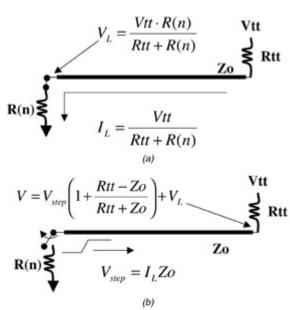

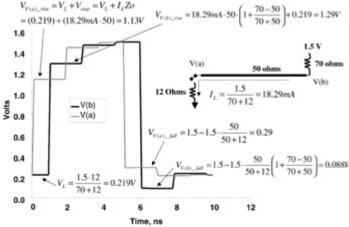

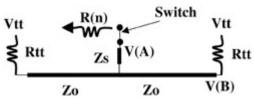

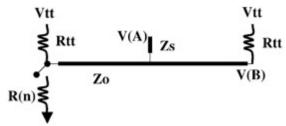

$$L = (\text{TD})(Z_o) = \sqrt{LC}\sqrt{\frac{L}{C}} = 7.130 \text{ nH}$$